#### **Buck Converter and Constant-Current Driver**

A.G.Dean ECE 460/560 Embedded System Architectures

# Switch-Mode Power Conversion and the Buck Converter

## How to Lower a Voltage from V<sub>in</sub> to V<sub>out</sub>

- Linear regulator

- Drops input voltage using "pass" transistor as variable resistor, converting extra power to heat.

- If output doesn't need as much power, reduce conductance of transistor (raise resistance), wasting more power.

- Switch-mode regulator

- Drops voltage by connecting and disconnecting input voltage very frequently

- If output doesn't need as much power, reduce duty cycle (fraction of time) input is connected.

- Minor additional power loss.

- Switches (transistors, diodes) are either on (very low resistance) or off (open circuit)

- Duty cycle typically controlled by pulse-width modulated (PWM) signal

- If needed, filter output voltage with capacitor

## **Energy Storage and Filtering**

- Convert energy between electrical and/or magnetic forms for efficient storage and filtering

- Use capacitors and inductors to store energy and filter out ripple

- Capacitors voltage is stabilized

- Inductors current is stabilized

- Capacitor stores energy as voltage difference

- $E = \frac{1}{2} CV^2$

- Total storage limited by voltage: need higher voltage

- Current affects charge/discharge rate, but not total energy storage

- Inductor stores energy as current and magnetic field

- $E = \frac{1}{2} LI^2$

- Total storage limited by current: need higher current

- Voltage affects charge/discharge rate, but not total energy storage

- Good match for low voltage operation. Easier to increase current capacity.

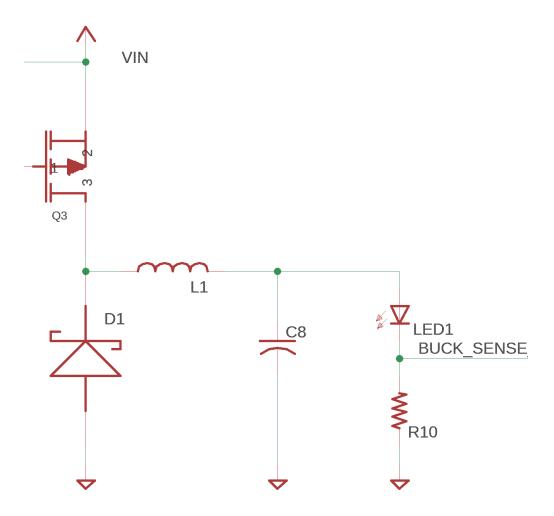

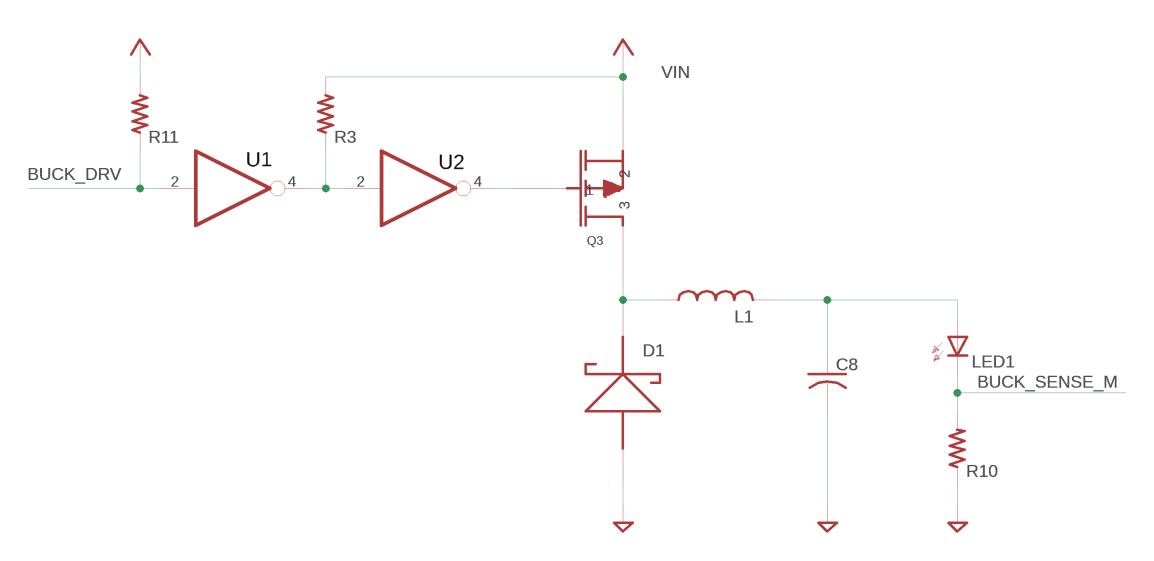

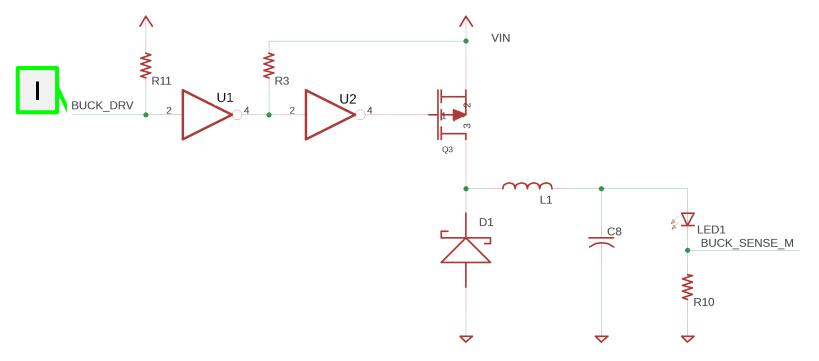

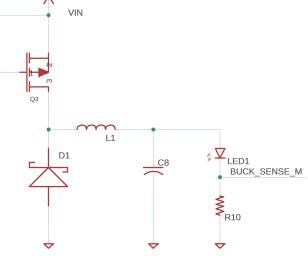

#### **Buck Converter Overview**

- PWM input signal

- Duty cycle determines control effort

- Switches

- Transistor Q3 is on when PWM signal on gate is active (low)

- Diode D1 is off when Q3 is on (controlled by voltage at Q/D/L node)

- Can add capacitor C8 on output to store some energy

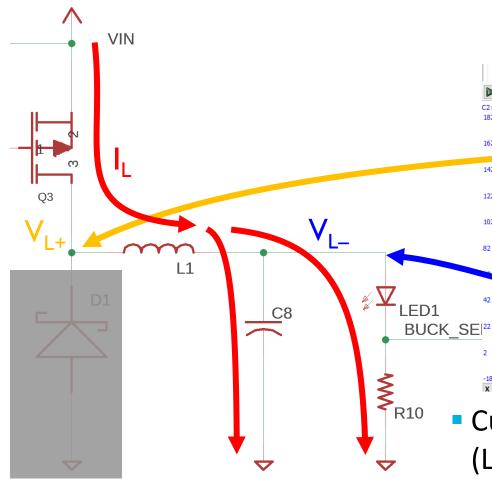

## Switch Q3 Closed

- Current flows through inductor L1 (ramping up) to load (LED1, C8)

- $di(t)/dt = (V_{L+}-V_{L-})/L$

- Slope depends on voltage applied across inductor

- Charges up L1 (inductor creates magnetic field) and C8

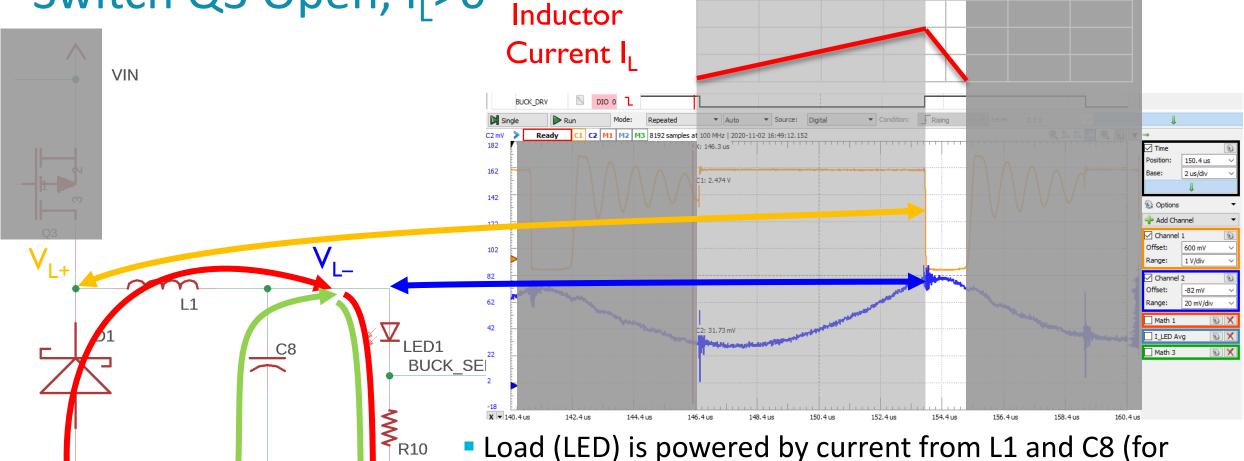

Switch Q3 Open, I<sub>L</sub>>0

- filtering

- Inductor current flows through D1 now, ramps down

- Larger load current will make I<sub>L</sub> ramp down faster

Switch Q3 Open,  $I_L = 0$

- Inductor current reaches 0, so now in discontinuous conduction mode

- Models (equations) get more complex

- Load is powered by C8

- Oscillation from L1 and parasitic capacitances of D1 and Q3

## **Switching Ripple**

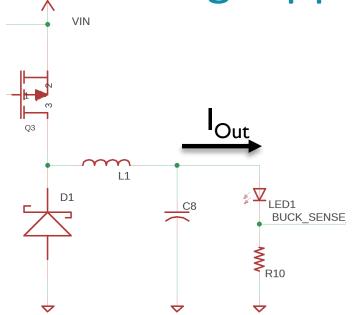

- Switching creates ripple in I<sub>L</sub>,V<sub>Out</sub>

- Output ripple voltage

- Depends on load current I<sub>Out</sub>, C8, switching frequency

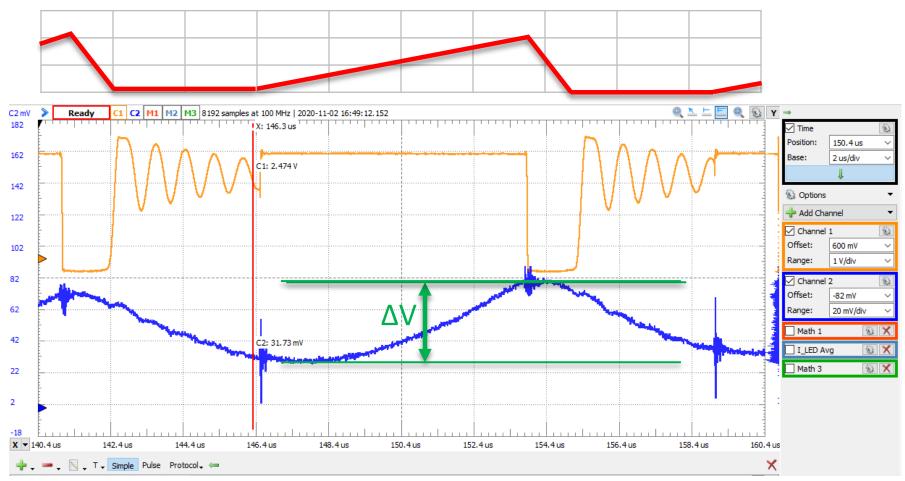

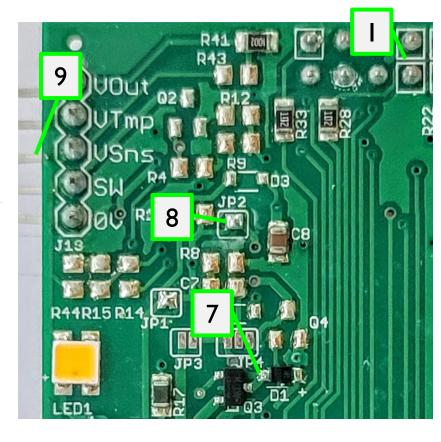

# Expansion Shield's Switch-Mode Power Converter

#### Shield Switch-Mode Power Converter Overview

- Used to convert power efficiently one voltage to another

- Configurable hardware

- Topology and function

- Buck converter (reduce voltage) we use this

- Boost converter (increase voltage)

- Noise control

- Snubber (R8, C7) to reduce EMI when Q3 switches on, off

- Switchable load transistor (Q2) for testing response to changes in load

- Feedback options

- Output voltage scaled by R9/(R9+R12). Single-ended (ground-referenced)

- Current out through LED1, scaled by R10 (2.2 mV/mA). Single-ended (ground-referenced)

- R10 selected to limit maximum current through LED1 to safer level

- Current out before capacitor C8, scaled by sense resistor R13. Differential (not ground-referenced)

## Schematic of SMPS Configured as Buck Converter

Optional undervoltage protection diode to keep Vout >= Vin - 3 V.

Target application: powering MCU and P3V3 rail from buck converter with Vin = 5 V (USB).

Vout stays above about 2 V (1.8 is the minimum)

Unused components are grayed or X'd out

Powered from 3V3. Used to isolate MCU GPIO from pull-up to Buck Vin.

Shorted solder jumper —

## Simplified Buck Converter Schematic

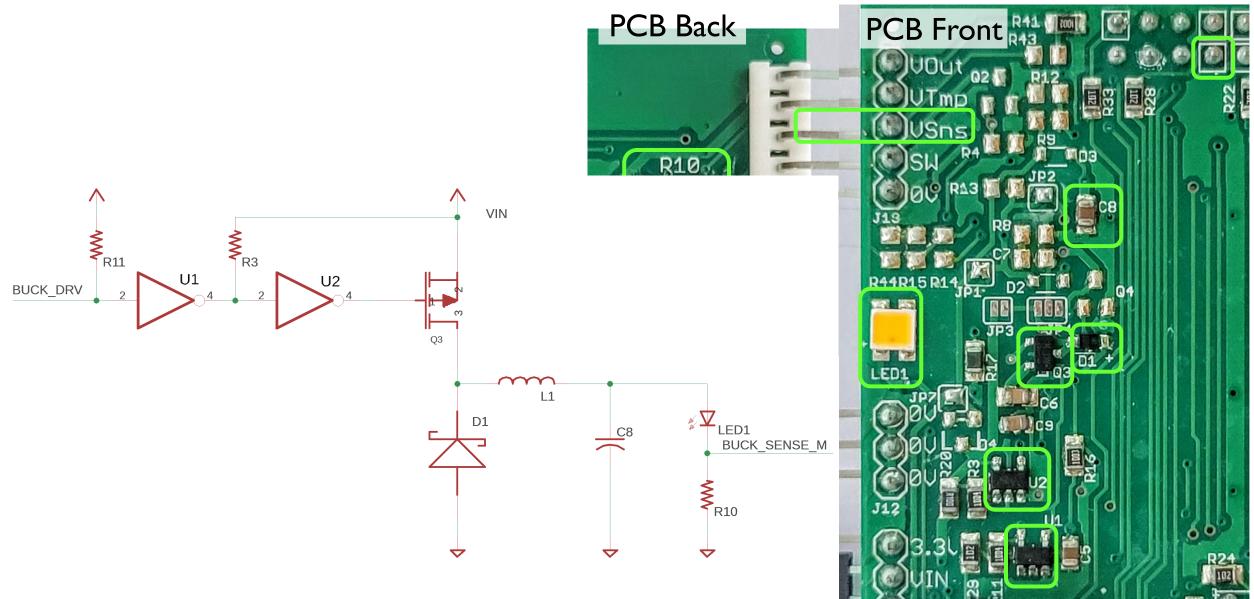

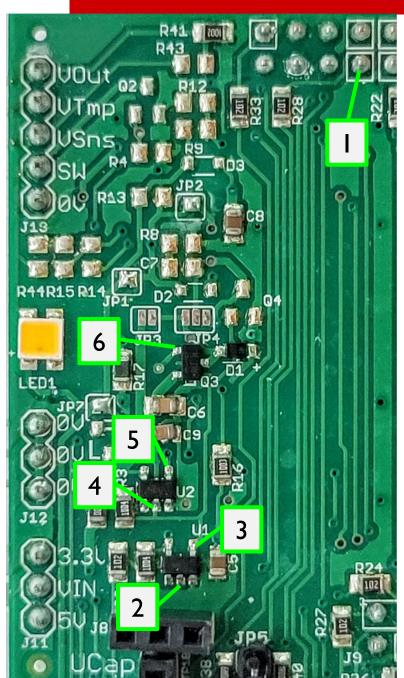

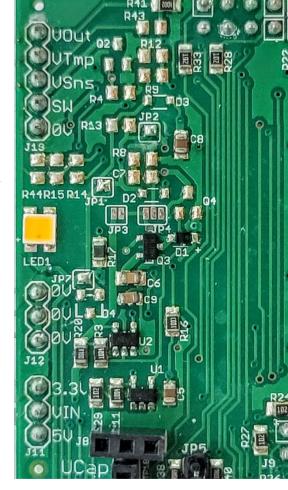

### **Buck Converter on PCB**

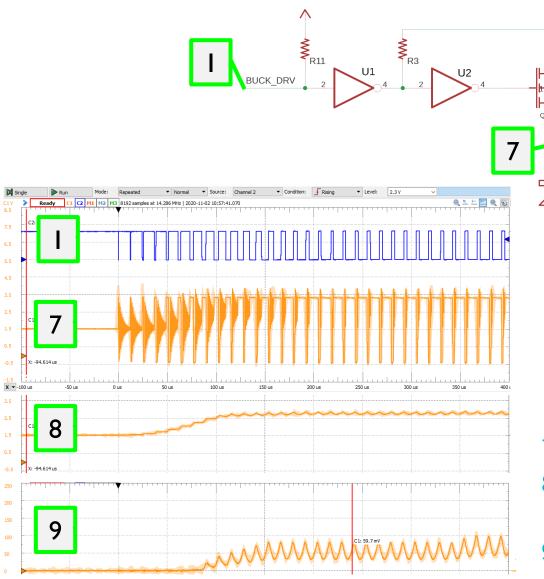

## Tracing the BUCK\_DRV PWM Signal

- 1. Confirm PWM signal at header pin

- 2. Confirm PWM signal at input to U3

- 3. Confirm inverted PWM signal at output of U3

- 4. Confirm inverted PWM signal at input to U1

- 5. Confirm PWM signal at output of U1

- 6. Confirm PWM signal at gate of Q3

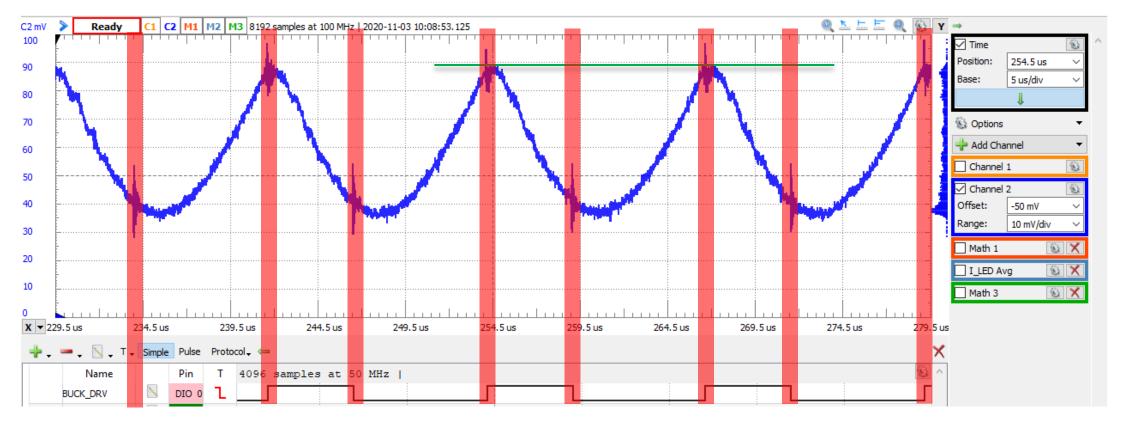

## **Buck Converter Power Stage Signals**

- Confirm switching signal at Q3/D1/L1 node. 1 V/division

- 8. Confirm output voltage at JP2 (L1/C8/LED1 node). 1V/division. *As C8 not used, will have large ripple.*

LED1 BUCK\_SENSE\_M

Confirm current sense voltage at BUCK\_SENSE\_M (S-). 50 mV/division. As C8 not used, will have large ripple.

## Visual, Resistance and Diode Tests – POWER OFF!

- Remove power and J11 jumper

- Visual checks. Confirm:

- All components in this schematic are present

- Solder connections to header pins are concave tents, not balls

- Dot on LED1 (anode) is closer to + (if not, LED is backwards)

- JP1 and JP2 are shorted

- Multimeter resistance tests

- J13 S- to 0V should be 2-3  $\Omega$ . If larger, check for bad soldering on R10, J13

- BUCK\_VIN to ground should be large (>1M, rising)

- Q3 pin 3 / D1 Anode / L1 node to ground should be large (>1M, rising)

- JP1 to ground should be large (>1M, rising)

- Multimeter diode tests

- D1 should show forward voltage of about 0.24 V

- LED1 should show forward voltage of about 2.46 V

- Q3

- + on Gate (2), on Drain (3) forward voltage 1 V

- + on Drain (3), on Gate (2) forward voltage 0.24 V

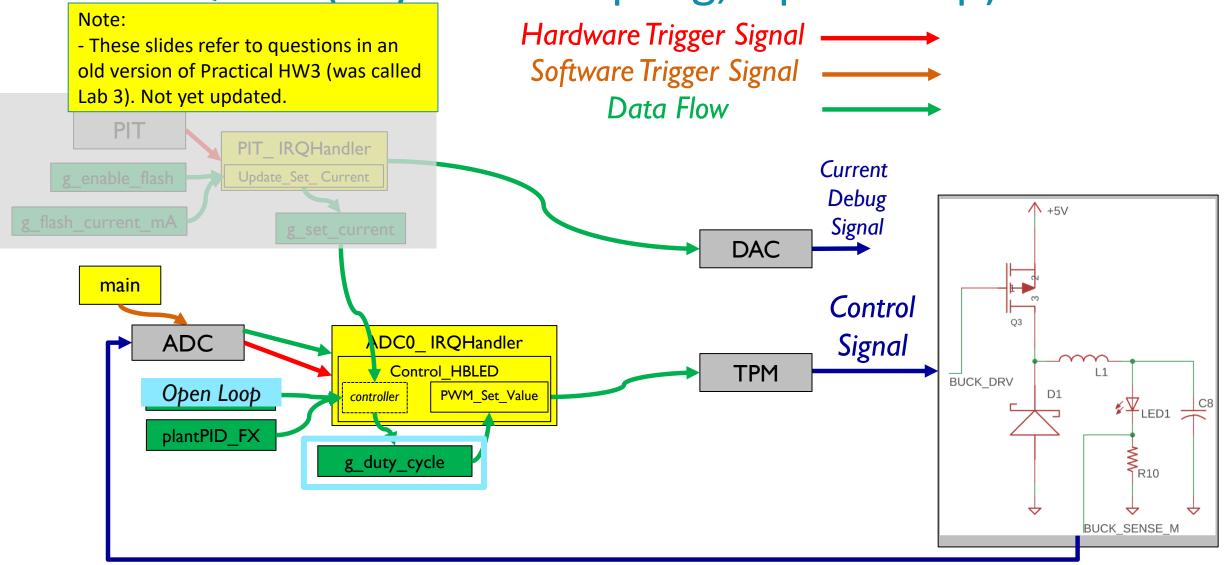

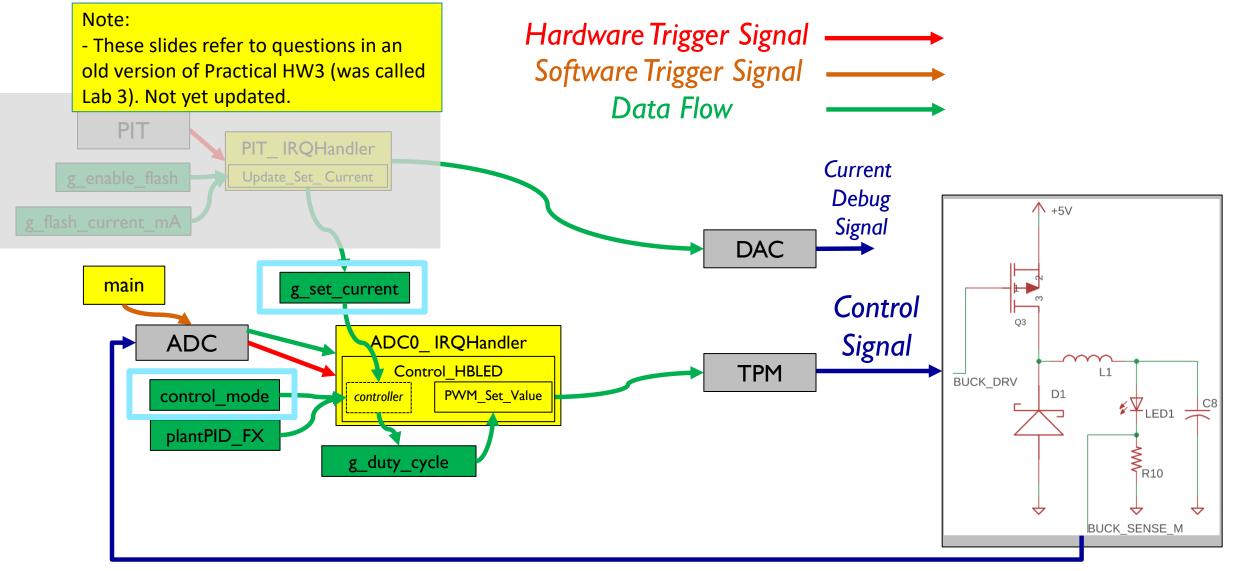

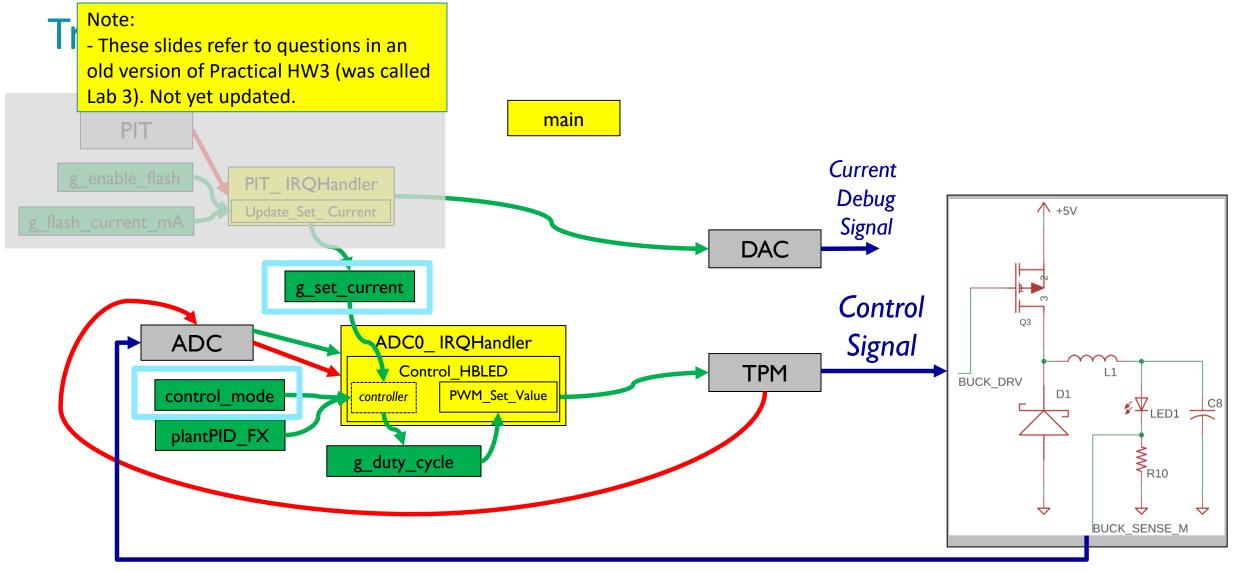

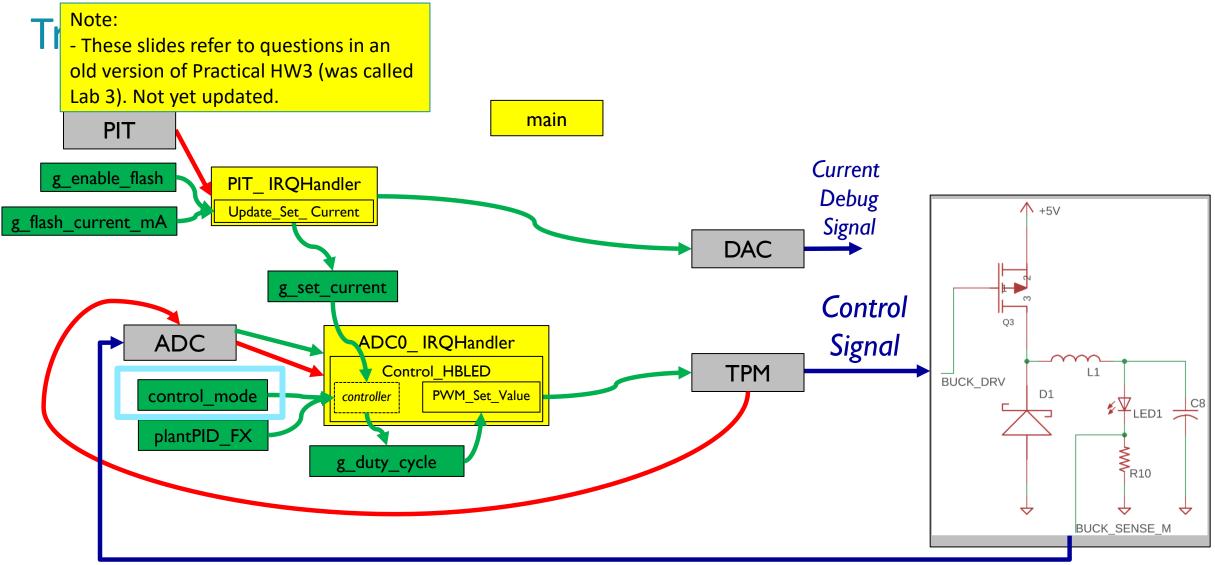

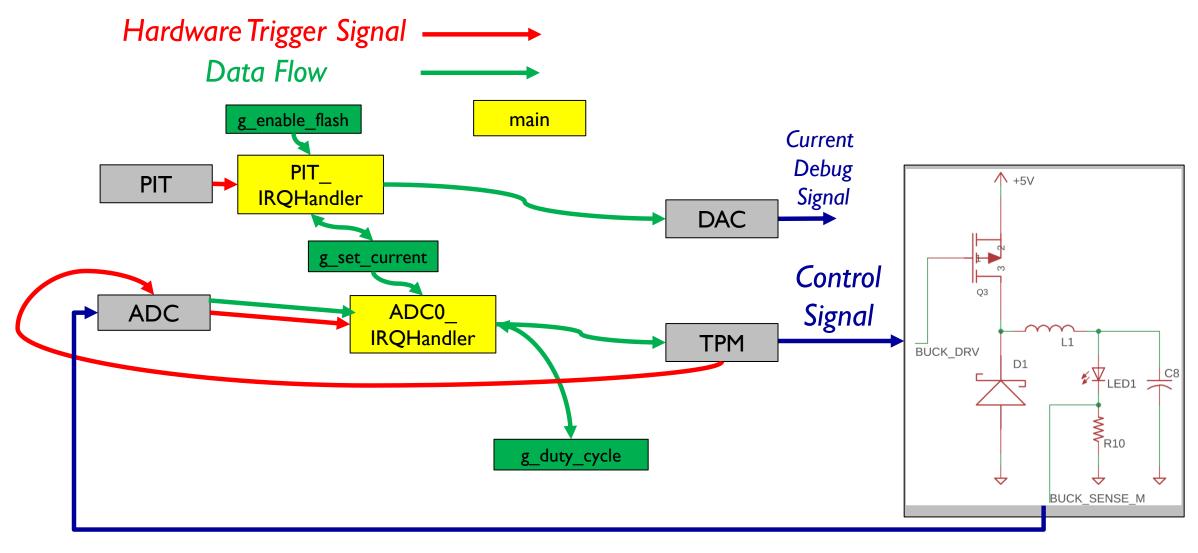

# Architecture for Constant Current HBLED Driver using Buck Converter

## Configuration in HBLED.h

- Control architectures available

- "Hard-Coded": Must rebuild code to change, since code for run-time changes would be too slow

- Asynchronous sampling

- Free-running S/W loop in main triggers ADC

- Synchronous sampling

- No frequency division:  $f_{ctl} = f_{sw} = f_{TPMO}$

- ADC hardware triggered by TPM0 overflow

- Software frequency division:  $f_{ctl} = f_{sw}/N = f_{TPMO}/N$

- N set by SW\_CTL\_FREQ\_DIV\_FACTOR

- ADC software triggered by TPM0 ISR

- Dual timers:  $f_{ctl} = f_{TPM2}$ ,  $f_{sw} = f_{TPM0}$

- TPM2 ISR enables TPM0 IRQ once

- TPM0 ISR software triggers ADC, disables TPM0 IRQ

- Controllers (compensators) available

- "Software-Configurable": Can change compensator and gains by tweaking variables as program runs

- Types

- None (open loop)

- Bang-Bang

- Incremental

- PID

- Fixed-point PID

- Parameters

- Gains are scaled by control loop period (faster update rate reduces the required gain)

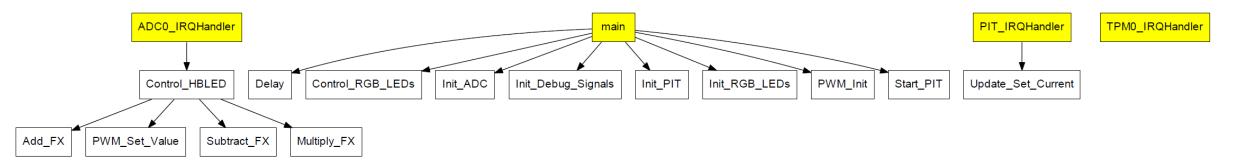

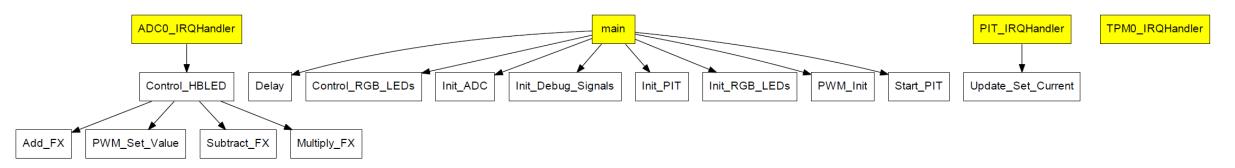

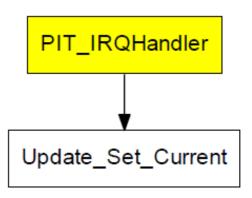

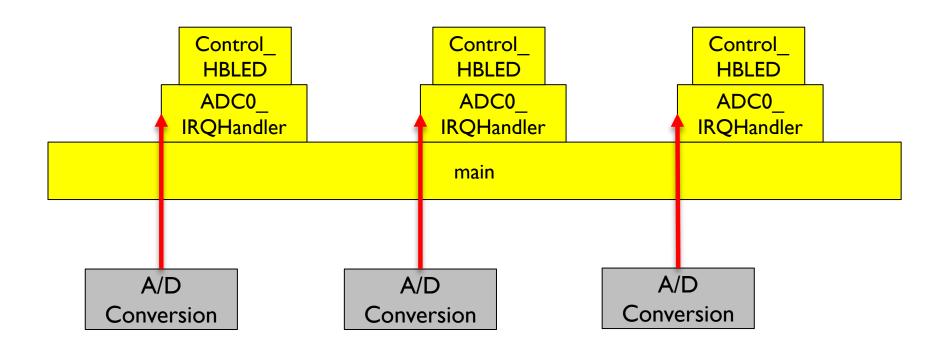

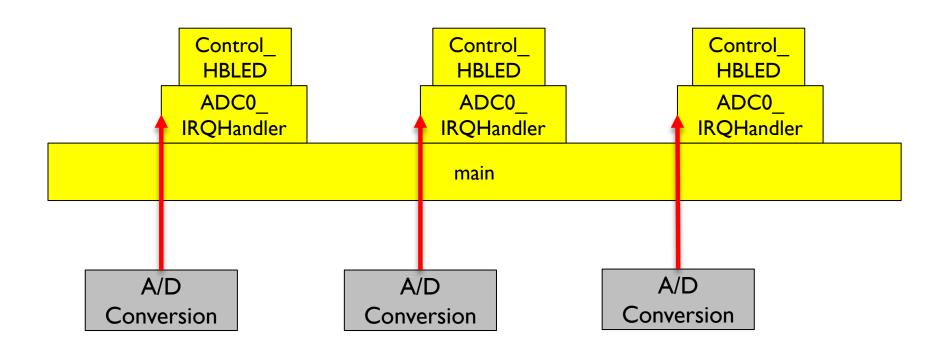

#### Which Functions Can Call Each Other?

#### Function Call Graph

- Functions in yellow are threads or interrupt handlers

- Calling behavior depends on the control architecture selected (USE\_SYNC\_SW\_CTL\_FREQ\_DIV shown here)

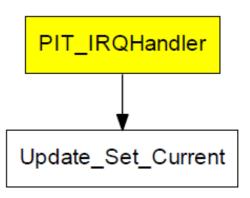

## Examining PIT\_IRQHandler

```

void PIT_IRQHandler() {

// check to see which channel triggered interrupt

if (PIT->CHANNEL[0].TFLG & PIT_TFLG_TIF_MASK) {

// clear status flag for timer channel 0

PIT->CHANNEL[0].TFLG &= PIT_TFLG_TIF_MASK;

// Do ISR work

Update_Set_Current();

} else if (PIT->CHANNEL[1].TFLG & PIT_TFLG_TIF_MASK) {

// clear status flag for timer channel 1

PIT->CHANNEL[1].TFLG &= PIT_TFLG_TIF_MASK;

}

}

```

- Global variable accesses

- Reads g\_enable\_flash

- Reads and writesg\_set\_current

- Peripheral access

- Writes to the DAC

- Note: compiler inlined call to Set\_DAC\_mA

```

void Update Set Current(void) {

static int delay=FLASH PERIOD;

if (g enable flash) {

delay--;

if (delay==1) {

FPTB->PSOR = MASK(DBG LED ON);

g set current = FLASH CURRENT MA;

Set DAC mA (g set current);

} else if (delay==0)

delay=FLASH PERIOD;

FPTB->PSOR = MASK (DBG LED ON);

g set current = FLASH CURRENT MA/4;

Set DAC mA (g set current);

} else {

FPTB->PCOR = MASK(DBG LED ON);

g set current = 0;

Set DAC mA (g set current);

```

```

void Set_DAC_mA(unsigned int current) {

unsigned int code = MA_TO_DAC_CODE(current);

// Force 16-bit write to DAC

uint16_t * dac0dat = (uint16_t *)&(DAC0->DAT[0].DATL);

*dac0dat = (uint16_t) code;

}

```

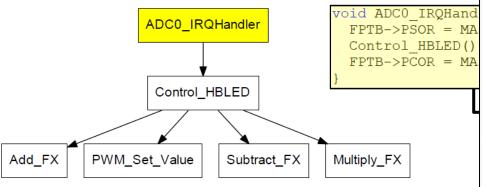

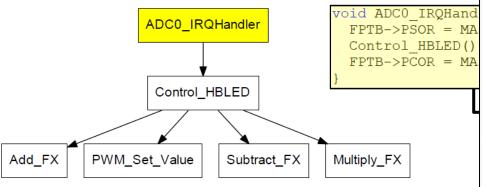

## Examining ADC0\_IRQ

- Global variable accesses

- Reads g set current

- Reads and writes g duty cycle

- Peripheral access

- Reads ADC0 result register

- Writes g duty cycle to TPM0

```

; // wait until end of conversion

#endif

res = ADC0 -> R[0];

measured current = (res*1500)>>16; // Extra Credit: Make this code work: V REF MV*MA SCALING N

switch (control mode) {

case OpenLoop:

// don't do anything!

break;

case BangBang:

if (measured current < g_set_current)</pre>

g duty cycle = LIM DUTY CYCLE;

else

g duty cycle = 0;

break;

case Incremental:

if (measured_current < g_set_current)</pre>

g_duty_cycle += INC_STEP;

else

g duty cycle -= INC STEP;

break;

case Proportional:

g duty cycle += (pGain 8*(g set current - measured current))/256; // - 1;

break;

case PID:

g duty cycle += UpdatePID(&plantPID, g set current - measured current, measured current);

break;

case PID FX:

error FX = INT TO FX(g set current - measured current);

change FX = UpdatePID FX(&plantPID FX, error FX, INT TO FX(measured current));

g duty cycle += FX TO INT(change FX);

break;

default:

break;

// Update PWM controller with duty cycle

if (g duty cycle < 0)

g duty cycle = 0;

else if (g duty cycle > LIM DUTY CYCLE)

g duty cycle = LIM DUTY CYCLE;

PWM Set Value (TPM0, PWM HBLED CHANNEL, g duty cycle);

FPTB->PCOR = MASK (DBG CONTROLLER);

```

## **Asynchronous Sampling**

## **ASYNC Sequence Diagram**

USE\_ASYNC\_SAMPLING

| m | ain A | DC | ADC<br>ISR | TPM0<br>Duty |

|---|-------|----|------------|--------------|

|   |       |    |            |              |

|   |       |    |            |              |

|   |       |    |            |              |

|   |       |    |            |              |

|   |       |    |            |              |

|   |       |    |            |              |

|   |       |    |            |              |

## **Timing Questions**

- How long does it take to do the whole control loop?

- How long does each individual part take?

- How stable is the timing?

- When do we really sample the input voltage?

- Can lead to under-estimate or over-estimate

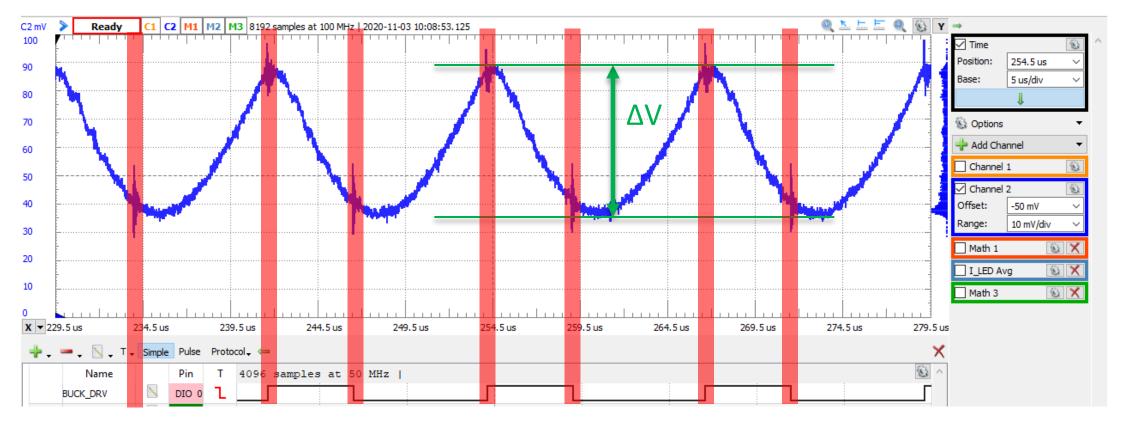

## When to Sample the LED Current?

- Need to sample in phase with BUCK\_DRV signal (PWM)

- Stay away from times of BUCK\_DRV transitions (noisy!)

- Same phase for each sample, otherwise may have error Edge-Aligned vs. Center-Aligned PWM of up to  $\Delta V$  in each sample

- Trigger with TPM

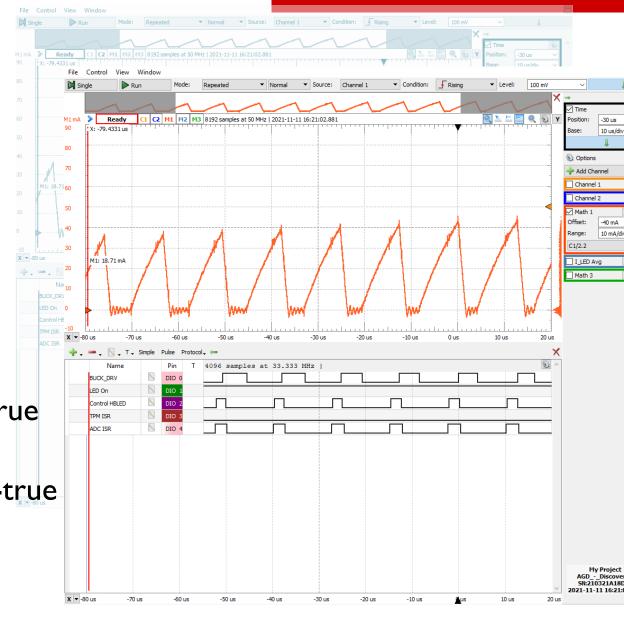

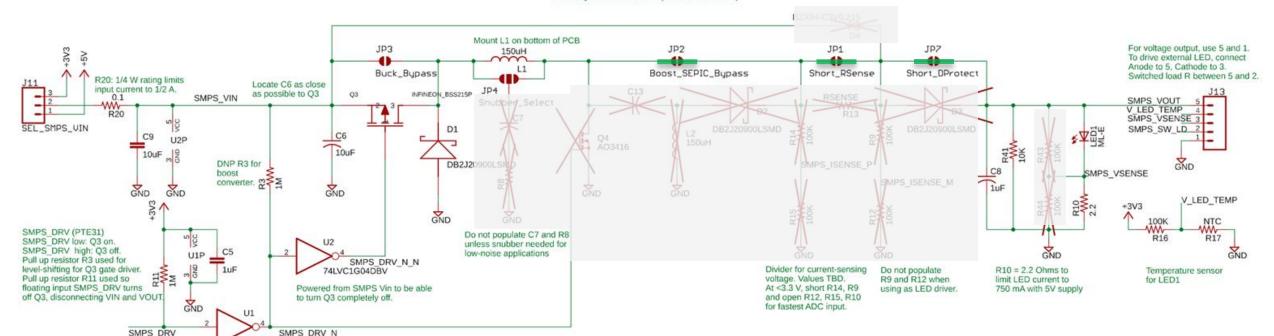

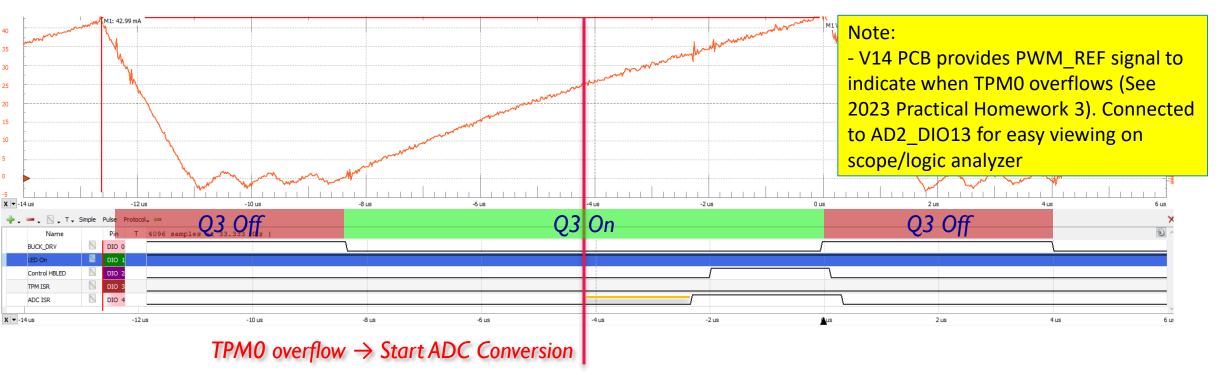

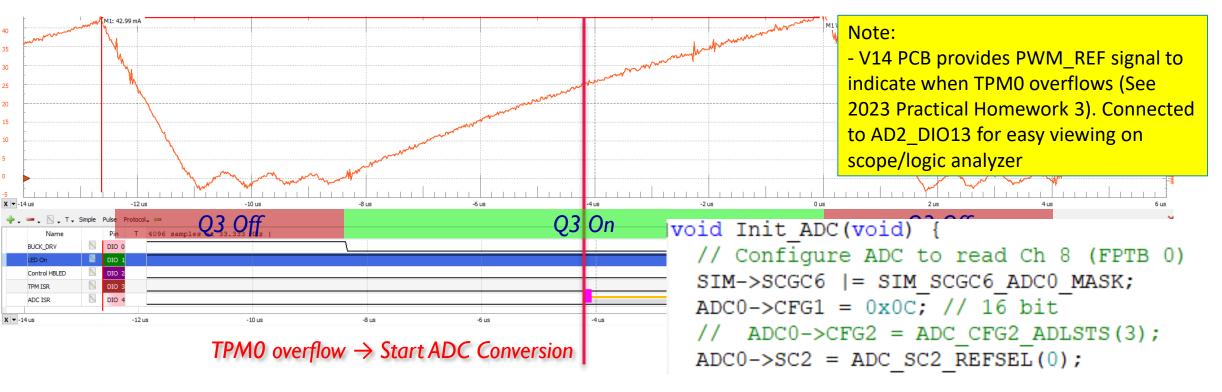

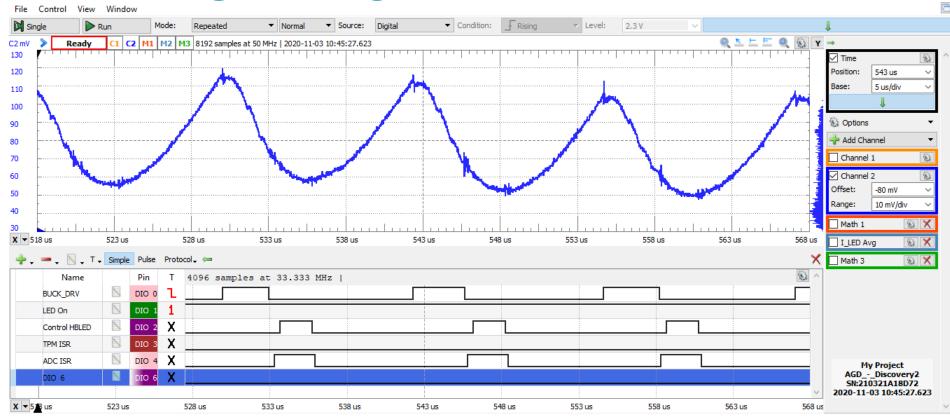

## **Examining Sampling Timing with Instrumentation**

- Signals monitored

- Current feedback shows current, noise

- BUCK\_DRV shows when transistor is on, off

- ADC\_ISR shows when ISR runs

- When does ADC sample the analog input?

- Starts a fixed time before the ADC\_ISR runs (assuming no interference from other interrupts)

- ADC conversion triggered by TPM0 overflow, which is in middle of transistor on time (BUCK\_DRV low)

## **Examining Sampling Timing with Instrumentation**

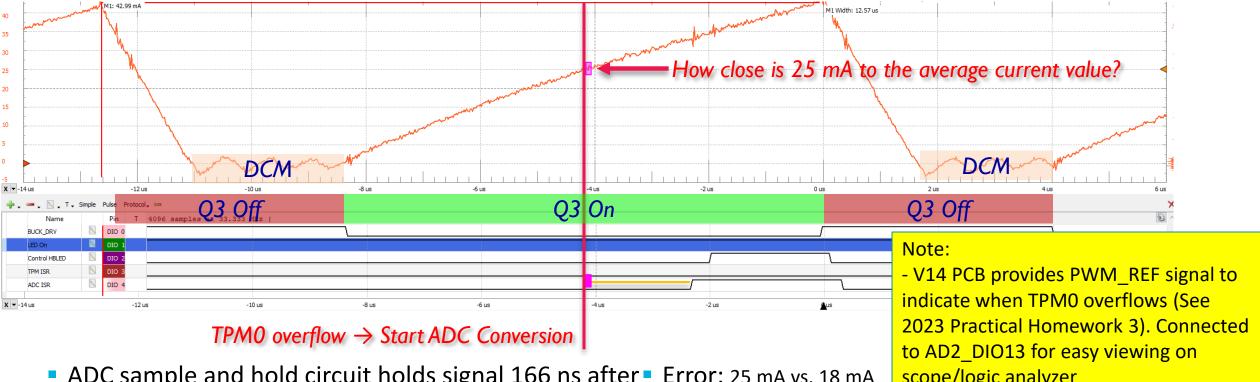

- How long is the sample time? Check source code, refer to MCU manual section on ADC

- Sample time is 4 ADCK cycles

- What is ADCK?

- 24 MHz (bus clock, no division)

- Sample time = 4/24 MHz = 166 ns ■

- BTW, ADCK is too fast to meet accuracy specifications (max 19 MHz)!

- Should set ADIV to 1 and ADHSC to 1 for 12 MHz ADCK

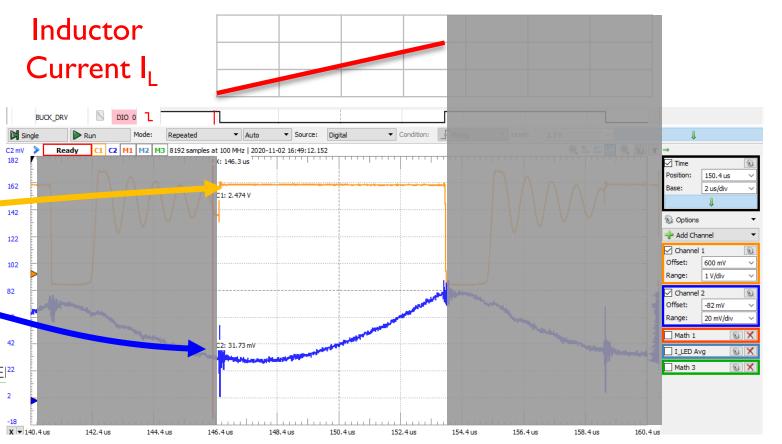

## Examining Sampling Timing with Instrumentation

- ADC sample and hold circuit holds signal 166 ns after Error: 25 mA vs. 18 mA start of conversion

- I<sub>LED</sub> = 25 mA at that point in time

- What is average value of this waveform?

- Estimate graphically: (area of triangle/area of full period rectangle) \* peak current ≈ 18 mA

- scope/logic analyzer

- Overestimates current by 39%

- Addressing error

- Adding filtering capacitor (C8) would reduce this

- Could scale reading, but depends on time spent in DCM (current oscillates around 0 mA). Need to evaluate stability of scaling across different duty cycles and load currents

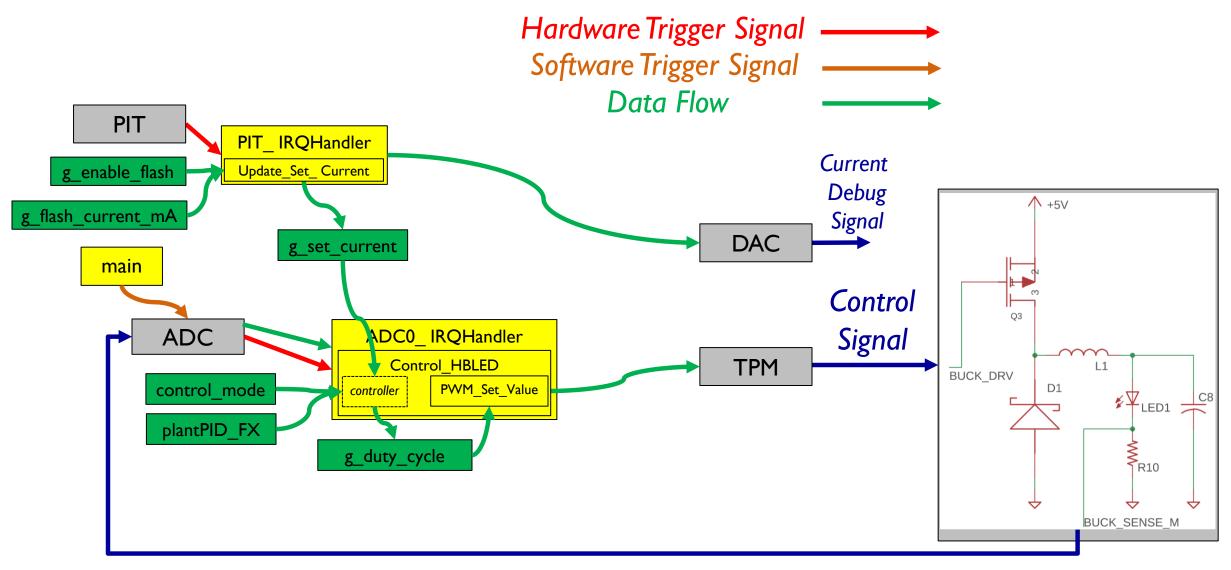

## Synchronous Sampling, No Frequency Division

USE SYNC NO FREQ DIV Hardware Trigger Signal ———— Data Flow main PIT Current PIT IRQHandler Debug Update\_Set\_ Current g enable flash 1 +5V Signal g\_flash\_current\_mA DAC g set current **Control ADC** ADC0 IRQHandler Signal Control HBLED **TPM** BUCK DRV PWM Set Value control mode controller ₹¥LED1 C8 plantPID\_FX g\_duty\_cycle BUCK SENSE M

# SYNC Sequence Diagram, No Division for F<sub>ctl</sub>

USE\_SYNC\_NO\_FREQ\_DIV

| ADC | ADC<br>ISR | TPM0<br>Duty | M0<br>uty |  |

|-----|------------|--------------|-----------|--|

|     |            |              |           |  |

|     |            |              |           |  |

|     |            |              |           |  |

|     |            |              |           |  |

|     |            |              |           |  |

|     |            |              |           |  |

|     |            |              |           |  |

|     | ADC        |              |           |  |

Lab 3: Q. 3-5 (Asynch. Sampling, Open-Loop)

Lab 3: Q. 6-7 (Asynch. Sampling, Closed-Loop, No Transients)

Lab 3: Q.8-10,13 (Synch. Sampling, Closed-Loop, No

Lab 3: Q.11-12, 14-15 (Synch. Sampling, Closed-Loop,

## SYNC Sequence Diagram, Software Division for F<sub>ctl</sub>

USE\_SYNC\_SW\_CTL\_FREQ\_DIV

| TPM0<br>(f <sub>sw</sub> ) | TPM0<br>ISR | ADC | ADC<br>ISR | TPM0<br>Duty |

|----------------------------|-------------|-----|------------|--------------|

|                            |             |     |            |              |

|                            |             |     |            |              |

|                            |             |     |            |              |

|                            |             |     |            |              |

|                            |             |     |            |              |

|                            |             |     |            |              |

|                            |             |     |            |              |

NC STATE UNIVERSITY

# SYNC Sequence Diagram, 2<sup>nd</sup> Timer for F<sub>ctl</sub>, ADC SW Trigger

(not in your code)

| ΓΡΜ0<br>Duty |

|--------------|

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

# SYNC Sequence Diagram, 2<sup>nd</sup> Timer for F<sub>ctl</sub>, ADC HW Trigger

(not in your code)

|   | $TPM2 \atop (f_{ctl})$ | TPM2<br>ISR | $TPM0$ $(f_{sw})$  | ADC | ADC<br>ISR | TPM0<br>Duty |  |

|---|------------------------|-------------|--------------------|-----|------------|--------------|--|

| _ | ('ctl)                 | 131         | (' <sub>sw</sub> ) | ADC | 1510       | Duty         |  |

|   |                        |             |                    |     |            |              |  |

|   |                        |             |                    |     |            |              |  |

|   |                        |             |                    |     |            |              |  |

|   |                        |             |                    |     |            |              |  |

|   |                        |             |                    |     |            |              |  |

|   |                        |             |                    |     |            |              |  |

|   |                        |             |                    |     |            |              |  |

|   |                        |             |                    |     |            |              |  |

|   |                        |             |                    |     |            |              |  |

|   |                        |             |                    |     |            |              |  |

### **How About Using DMA?**

(not in your code)

Replace TPM2 ISR with DMA transfer to enable ADC hardware trigger

| TPM2<br>(f <sub>ctl</sub> ) | DMA | TPM0<br>(f <sub>sw</sub> ) | ADC | ADC<br>ISR | TPM0<br>Duty |  |

|-----------------------------|-----|----------------------------|-----|------------|--------------|--|

|                             |     |                            |     |            |              |  |

|                             |     |                            |     |            |              |  |

|                             |     |                            |     |            |              |  |

|                             |     |                            |     |            |              |  |

|                             |     |                            |     |            |              |  |

|                             |     |                            |     |            |              |  |

# Old Diagrams and Notes

### Why Use Switch-Mode? Efficiency

#### Linear regulator

- Drops input voltage using "pass" transistor as variable resistor, converting extra power to heat.

- If output doesn't need as much power, reduce conductance of transistor (raise resistance), wasting much more power.

- Switch-mode regulator

- Drop voltage by connecting and disconnecting input voltage very frequently (faster than load circuit can notice) to create lower average output voltage.

- If output doesn't need as much power, reduce duty cycle (fraction of time) input is connected. Minor additional power loss.

- Switches (transistors, diodes) are either on (very low resistance) or off (open circuit)

- Duty cycle typically controlled by pulse-width modulated (PWM) signal

- If needed, filter output voltage to smooth it

### **NC STATE** UNIVERSITY

## **Energy Storage and Filtering**

- Use capacitors and inductors to store energy and filter out ripple

- Capacitors can't instantaneously change voltage

- Inductors can't instantaneously change current

- Power converted between electrical and magnetic forms for efficient storage and filtering

- Capacitor stores energy as voltage difference

- $E = \frac{1}{2} CV^2$

- Total storage limited by voltage: need higher voltage

- Current affects charge, discharge rate, but not total energy storage

- Inductor stores energy as current and magnetic field

- $E = \frac{1}{2} LI^2$

- Total storage limited by current: need higher current

- Voltage affects charge, discharge rate, but not total energy storage

- Good match for low voltage operation. Easier to increase current capacity.

### When to Sample the LED Current?

- Need to sample in phase with BUCK\_DRV signal (PWM)

- Same phase for each sample, otherwise may have error of up to  $\Delta V$  in each sample

- Trigger with TPM

- Stay away from times of BUCK\_DRV transitions, since they are noisy

### Hardware and Software Overview

**Current Feedback Signal**

### Which Functions Can Call Each Other?

### Function Call Graph

Functions in yellow are threads or interrupt handlers

### Examining ADC0\_IRQ

- Global variable accesses

- Reads g\_set\_current

- Reads and writes g duty cycle

- Peripheral access

- Reads ADC0 result register

- Writes g duty cycle to TPM0

```

; // wait until end of conversion

#endif

res = ADC0 -> R[0];

measured current = (res*1500)>>16; // Extra Credit: Make this code work: V REF MV*MA SCALING N

switch (control mode) {

case OpenLoop:

// don't do anything!

break;

case BangBang:

if (measured current < g set current)</pre>

g duty cycle = LIM DUTY CYCLE;

g duty cycle = 0;

break;

case Incremental:

if (measured current < g set current)</pre>

g duty cycle += INC STEP;

else

g duty cycle -= INC STEP;

break;

case Proportional:

g duty cycle += (pGain 8*(g set current - measured current))/256; // - 1;

break;

case PID:

g duty cycle += UpdatePID(&plantPID, g set current - measured current, measured current);

break;

case PID FX:

error FX = INT TO FX(g set current - measured current);

change FX = UpdatePID FX(&plantPID FX, error FX, INT TO FX(measured current));

g duty cycle += FX TO INT(change FX);

break;

default:

break;

// Update PWM controller with duty cycle

if (g duty cycle < 0)

g duty cycle = 0;

else if (g duty cycle > LIM DUTY CYCLE)

q duty cycle = LIM DUTY CYCLE;

PWM Set Value (TPMO, PWM HBLED CHANNEL, g duty cycle);

FPTB->PCOR = MASK (DBG CONTROLLER);

```

### Examining PIT\_IRQHandler

```

void PIT_IRQHandler() {

// check to see which channel triggered interrupt

if (PIT->CHANNEL[0].TFLG & PIT_TFLG_TIF_MASK) {

// clear status flag for timer channel 0

PIT->CHANNEL[0].TFLG &= PIT_TFLG_TIF_MASK;

// Do ISR work

Update_Set_Current();

} else if (PIT->CHANNEL[1].TFLG & PIT_TFLG_TIF_MASK) {

// clear status flag for timer channel 1

PIT->CHANNEL[1].TFLG &= PIT_TFLG_TIF_MASK;

}

}

```

- Global variable accesses

- Reads g\_enable\_flash

- Reads and writesg\_set\_current

- Peripheral access

- Writes to the DAC

- Note: compiler inlined call to Set\_DAC\_mA

```

void Update Set Current(void) {

static int delay=FLASH PERIOD;

if (g enable flash) {

delay--;

if (delay==1) {

FPTB->PSOR = MASK(DBG LED ON);

g set current = FLASH CURRENT MA;

Set DAC mA (g set current);

} else if (delay==0)

delay=FLASH PERIOD;

FPTB->PSOR = MASK (DBG LED ON);

g set current = FLASH CURRENT MA/4;

Set DAC mA (g set current);

} else {

FPTB->PCOR = MASK(DBG LED ON);

g set current = 0;

Set DAC mA (g set current);

```

```

void Set_DAC_mA(unsigned int current) {

unsigned int code = MA_TO_DAC_CODE(current);

// Force 16-bit write to DAC

uint16_t * dac0dat = (uint16_t *)&(DAC0->DAT[0].DATL);

*dac0dat = (uint16_t) code;

}

```

# Rough Timing Diagram

Does it really look like this?

### **Examining Timing with Instrumentation**

- How long does it take to do the whole control loop?

- How long does each individual part take?

- How stable is the timing?

- When do we really sample the input voltage?

**Examining Timing with Instrumentation**

- Hardware signals

- BUCK DRV: when does cycle start, end

- Current feedback: see where the noise is

- Software-generated signals

- ADC ISR: when does AD conversion finish, ISR start

- Control\_HBLED: when control loop runs

- LED On: helps with filtering triggers

- Would right control mode let us see signals better?

- How to trigger?

- Using center-aligned PWM, so not ideal to trigger off rising or falling edge of BUCK\_DRV

- PIT ISR interference with ADC ISR

### Rough Timing Diagram

Does it really look like this?

#### File Control View Window ▼ Condition: Fising ▼ Level: 100 mV ▼ Source: Channel 1 Ready C1 C2 M1 M2 M3 8192 samples at 50 MHz | 2021-11-11 16:17:47.265 👰 💆 🗮 💆 👰 🔞 🔻 -30 us 10 us/div X: -35.7545 us Options - Add Channel Channel 1 Channel 2 ✓ Math 1 Offset: Range: 10 mA/div C1/2.2 I\_LED Avg Math 3 M1: 1.384 mA X ▼ -80 us -70 us -60 us -50 us -40 us -30 us -20 us -10 us 0 us 10 us 💠 🗸 🔼 T T Simple Pulse Protocol 🗢 4096 samples at 33.333 MHz DIO 0 BUCK\_DRV Old: low-true LED On DIO Control HBLED DIO TPM ISR ADC ISR DIO 4 BUCK\_DRV New: high-true DIO 1 LED On Control HBLED DIO 3 TPM ISR ADC ISR DIO 4 My Project AGD\_-\_Discovery2 SN:210321A18D72 2021-11-11 16:17:47.265 10 us

### **NC STATE UNIVERSITY**