# 18: Scope Designs on Platform 1

**v**3

l v3

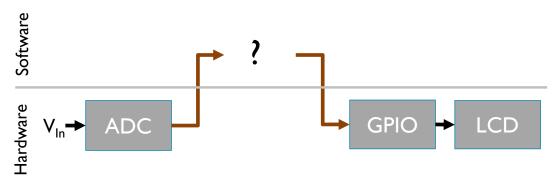

# **Analog Scope Example**

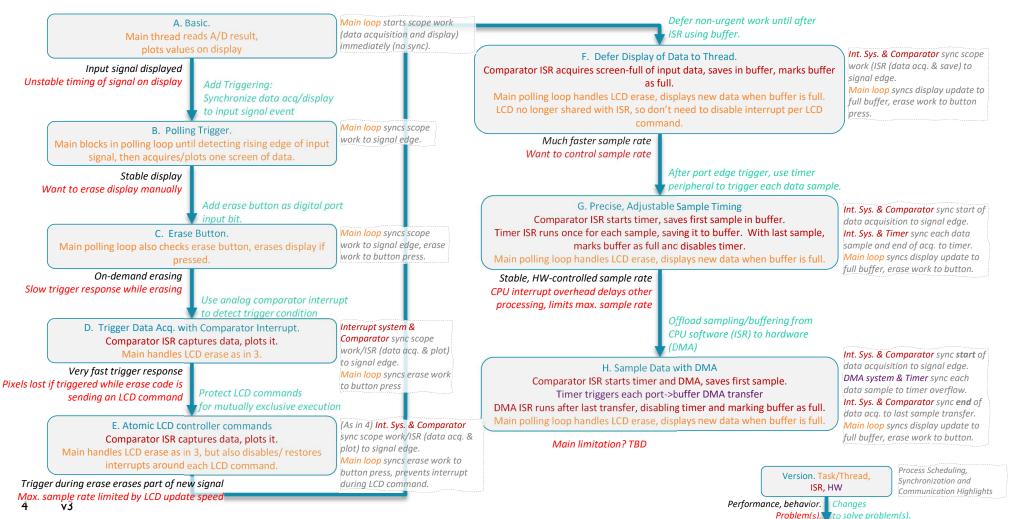

# Overview of Scope Design Evolution: What and Why

# A. Basic. Main thread reads A/D result, plots values on display

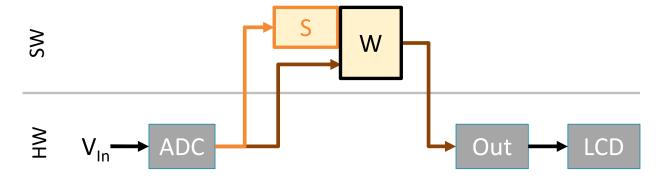

#### Add synchronization

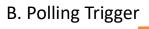

#### B. Polling Trigger.

Main blocks awaiting rising edge of input signal, then acquires/plots one screen of data.

#### Add feature

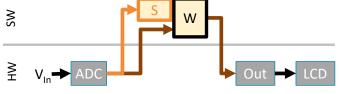

#### C. Erase Button.

Main polling loop also checks erase button, erases display if pressed.

Improve responsiveness of synchronization

Reduce timing interference to other SW

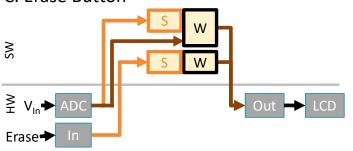

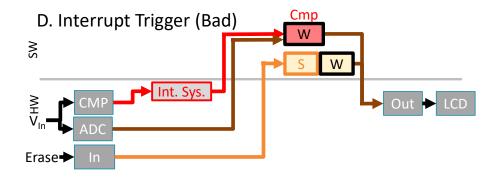

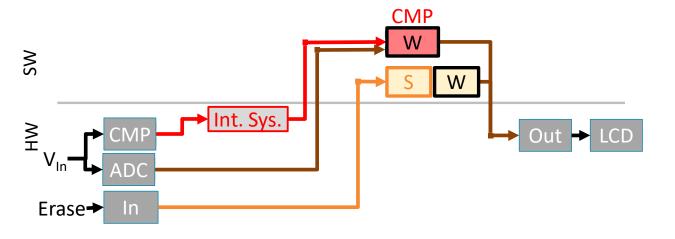

D. Trigger Data Acq. with Comparator Interrupt.

Comparator ISR captures data, plots it.

Main handles LCD erase as in 3.

#### Share hardware safely

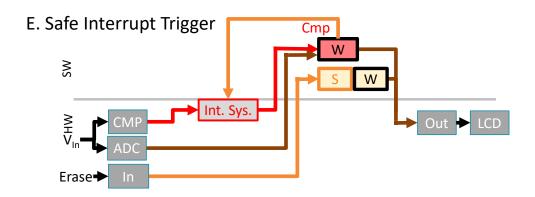

E. Atomic LCD controller commands

Comparator ISR captures data, plots it.

Main handles LCD erase as in 3, but also disables/ restores interrupts around each LCD command.

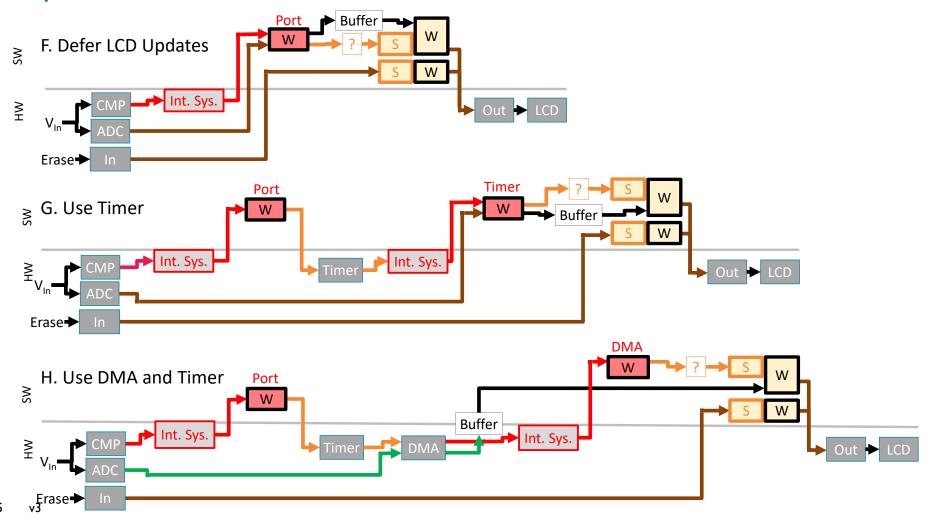

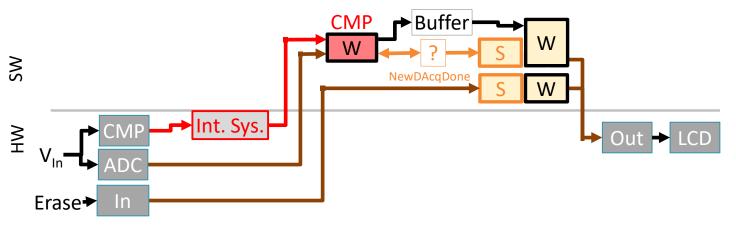

#### F. Defer Display of Data to Thread.

Comparator ISR acquires all input data, saves in buffer, marks buffer as full.

Main polling loop handles LCD erase, displays new data when buffer is full.

LCD no longer shared with ISR, so less sync needed.

Stable, adjustable timing for input sampling

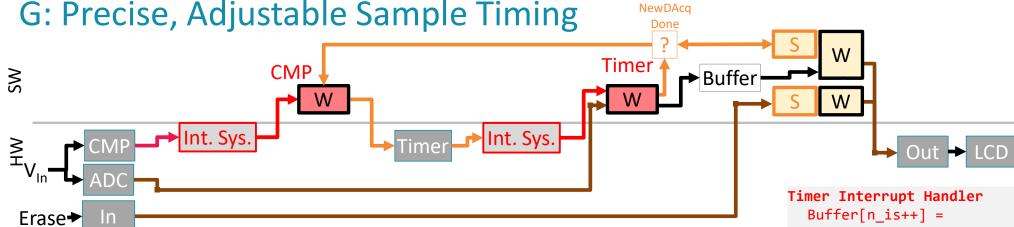

#### G. Precise, Adjustable Sample Timing

Comparator ISR starts timer, saves first sample in buffer.

Timer ISR runs once for each sample, saving it to buffer.

With last sample, marks buffer as full and disables timer.

Main polling loop erases LCD, displays new data when buffer is full.

Allow faster input sampling rates

Further stabilize timing for input sampling

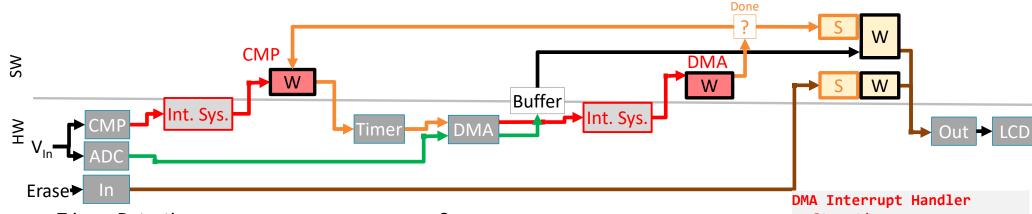

#### H. Sample Data with DMA

Comparator ISR starts timer and DMA, saves first sample.

Timer triggers each port->buffer DMA transfer

DMA ISR runs after last transfer, disabling timer, marking buffer as full.

Main polling loop erases LCD, displays new data when buffer is full.

Allow faster input sample rates by deferring plotting work, reducing sync needed

Version. Task/Thread, ISR, HW

# Detailed Overview of Scope Designs: What and Why

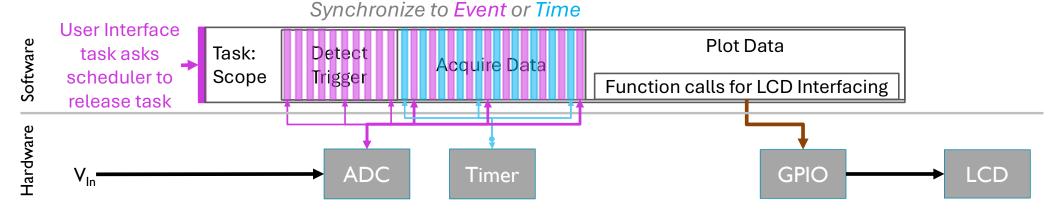

# I/O-Driven Synchronization Requirements for Scope

- First synchronization

- Task starts after UI asks scheduler to release it

- Detect Trigger: 2<sup>nd</sup> set of synchronizations

- Start A/D conversion

- Sync to A/D conversion complete, read result, analyze, decide if trigger condition met or need to repeat

- Acquire Data: 3<sup>rd</sup> set of synchronizations

- Sync to time (periodic) for next sample, start A/D conversion

- Sync to A/D conversion complete, read result, analyze, decide if trigger condition met or need to repeat

- Plot data on LCD: No sync needed

- LCD controller faster than software & GPIO interface

- Simplify for design examples A-G

- Eliminate sync to A/D conversion by assuming fast ADC: one A/D conversion per CPU instruction, nonstop conversions.

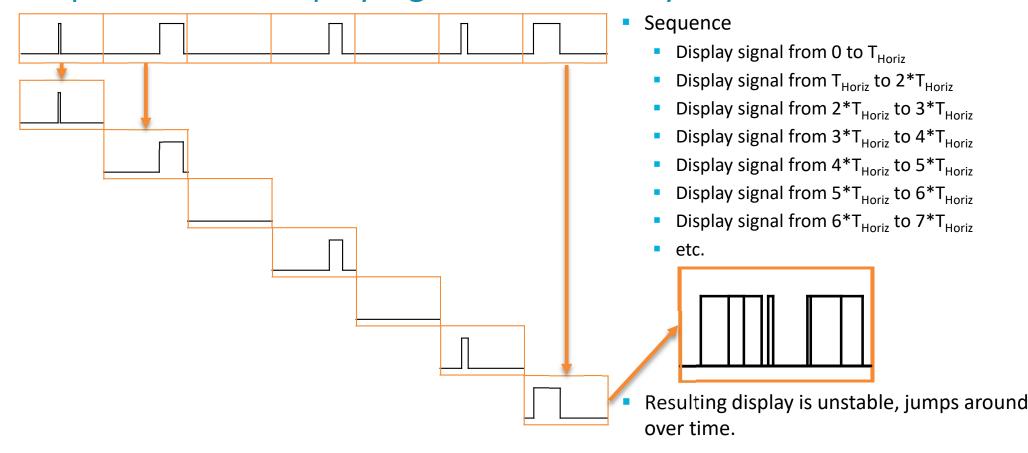

# Scope Triggering: Synchronizing Data Acquisition to Input Signal Activity

# Synchronization: Simple Oscilloscope Example

- Input signal

- Pulses with irregular start times, changing pulse widths

- Displaying the signal

- Oscilloscope ("scope") plots signal value (e.g. voltage) vertically vs. time horizontally

- Horizontal time base determines amount of time (T<sub>Horiz</sub>) represented on scope display

- Display stability depends timing relationship between when scope starts displaying the signal, and when the signal changes

- "Infinite persistence" accumulates all acquired traces on display until erase button is pressed

# Simple Method: Display Signal Continuously

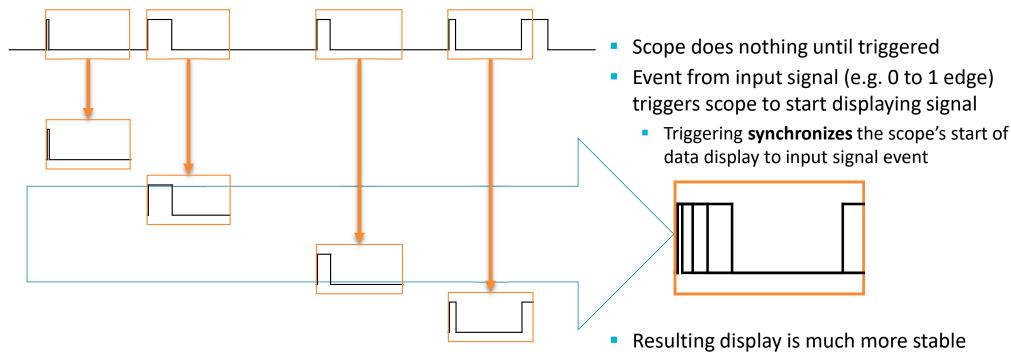

# Stabilize Display with Triggering

- Rising edge of signal is stable

- Except for last acquisition, where time between rising edges < T<sub>horiz</sub>

- Falling edge is not stable, because pulse width varies

# Implementation of Scope with Triggering

- Behavior

- Display signal voltage on LCD, synchronized to signal's rising edge through threshold

- Simplify: Ignore erasing previous acquisition from LCD. Ignore user controls

- Hardware Components

- Analog to Digital converter: Fast enough to keep up with MCU: 48 Msamples/second. (NOT the ADC on the KL25Z)

- Microcontroller: KL25Z

- LCD: 320x240 display with controller

- Basic flow of operations

- Wait for/detect V<sub>in</sub> rising through V<sub>threshold</sub>

- Rising Edge: V<sub>in</sub>(previous sample) < V<sub>threshold</sub> AND

V<sub>in</sub>(current sample) >= V<sub>threshold</sub>

- Loop to Acquire N data samples and display them

- Sample ADC: acquisition[n] = ADC\_data

- Scale acquisition[n], plot on LCD until reaching end of display

# Scope Design Version: Process and Synchronization Summary

| Process           | Erase Display             |                  |  |  |  |

|-------------------|---------------------------|------------------|--|--|--|

| Design<br>Version | Sync:<br>Trigger<br>Erase | Erase<br>Display |  |  |  |

| Α                 | -                         |                  |  |  |  |

| В                 | -                         |                  |  |  |  |

| С                 | Main thread               |                  |  |  |  |

| D, E              | Main thread               |                  |  |  |  |

| F                 | Main thread               |                  |  |  |  |

| G                 | Main thread               |                  |  |  |  |

| Н                 | Main thread               |                  |  |  |  |

| Acquire and Plot Data  |                                           |                         |               |                                     |             |  |  |

|------------------------|-------------------------------------------|-------------------------|---------------|-------------------------------------|-------------|--|--|

| Sync: Trigger<br>Scope | Sync: Schedule<br>A/D Conversion<br>Start | Start A/D<br>Conversion | Read ADC Data | Sync: Indicate<br>Data Acq.<br>Done | Plot Data   |  |  |

| -                      | -                                         | Main thread             |               |                                     |             |  |  |

| Main thread            | -                                         | Main thread             |               |                                     |             |  |  |

| Main thread            | -                                         | Main thread             |               |                                     |             |  |  |

| Comparator             | -                                         | Comparator ISR          |               |                                     |             |  |  |

| Comparator             | -                                         | Comparator ISR Mai      |               |                                     |             |  |  |

| Comparator             | Timer                                     | Timer ISR Main          |               |                                     |             |  |  |

| Comparator             | Timer                                     | Timer                   | DMA           | DMA ISR                             | Main thread |  |  |

Software: Thread

Software: ISR / IRQ

Handler

Hardware:

Peripheral

# Scope Example Processes: Alternate View

| Ver. | Software                                                           |                                |                | Hardware |                             |                    |                |

|------|--------------------------------------------------------------------|--------------------------------|----------------|----------|-----------------------------|--------------------|----------------|

|      | Threads                                                            | ISRs                           |                |          |                             |                    |                |

|      | Main                                                               | Comparator                     | Timer          | DMA      | Comparator                  | Timer              | DMA            |

| Α    | Sample, Display                                                    |                                |                |          |                             |                    |                |

| В    | Detect Trigger Condition, Sample,<br>Display                       |                                |                |          |                             |                    |                |

| С    | Detect Trigger Condition, Sample,<br>Update Display, Erase Display |                                |                |          |                             |                    |                |

| D, E | Erase Display                                                      | Take Sample,<br>Update Display |                |          | Detect Trigger<br>Condition |                    |                |

| F    | Erase Display, Update Display                                      | Take Sample                    |                |          | Detect Trigger<br>Condition |                    |                |

| G    | Erase Display, Update Display                                      |                                | Take<br>Sample |          | Detect Trigger<br>Condition | Schedule<br>Sample |                |

| Н    | Erase Display, Update Display                                      |                                |                |          | Detect Trigger<br>Condition | Schedule<br>Sample | Take<br>Sample |

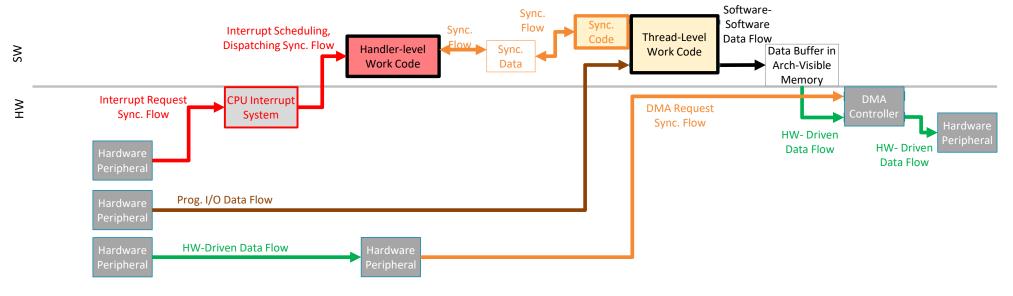

# Diagram Syntax

Boxes: Processes, code, and data objects

Do Work Process (thread or handler (interrupt service routine))

Synchronization Code (includes scheduling, dispatching at this level)

Interrupt System (includes scheduling, dispatching at this level)

Synchronization data object

Data buffer in architecturally-visible memory, available to software and hardware

**Arrows: Data and Synchronization (Control) Flows**

Software activity data flow

Programmed I/O data flow (software-driven)

Hardware activity data flow (hardware-driven)

Synchronization flow

Interrupt flow

# **Scope Evolution**

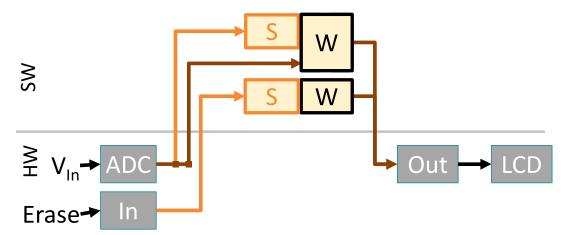

#### C. Erase Button

Synchronous Input for Trigger Detection

# **Scope Evolution**

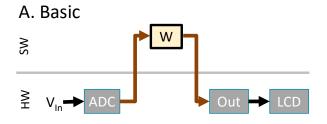

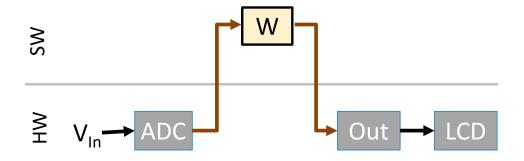

# A. No Trigger Detection

- Synchronize to trigger condition: None

- Schedule: Implicit

- Dispatch: Implicit

# Thread ... // No Detector/Synchronizer // No Scheduler // No Dispatcher // Handler process for (x=n=0; n<NS; n++) { r = ADC->Result; y = scale(r); LCD\_Plot(x++, y, tr\_clr); } LCD\_Plot(px, py, pcolor){ Draw rectangle from (px, py) to (px, py) with pcolor }

# B. Polling Trigger Detection with Busy-Wait Loop

- Synchronize to trigger condition: Loop in thread analyzes ADC results

- Schedule: Implicit SW in thread

- Dispatch: Implicit SW in thread

```

Thread

...

// Detector/Synchronizer

while (ADC->Result < V_Threshold)

;

// No Scheduler

// No Dispatcher

// Handler process

for (x=n=0; n<NS; n++) {

r = ADC->Result;

y = scale(r);

LCD_Plot(x++, y, tr_clr);

}

```

#### C. Add Erase Button

#### Trigger

- Synchronize: Polling/analysis loop in thread

- Schedule: SW in thread

- Dispatch: Subroutine call

#### Erase

- Synchronize: Polling/analysis test in thread

- Schedule: SW test

- Dispatch: Subroutine call

```

Thread(s)

...

// Detector/Synchronizer

while (ADC->Result < V_Threshold) {

if (Erase_Pressed)

LCD_Erase();

}

// Do Work: Acquire data

for (x=n=0; n<NS; n++) {

r = ADC->Result;

y = scale(r);

LCD_Plot(x++, y, tr_clr);

}

```

```

LCD_Plot(px, py, pcolor){

Draw rectangle from (px, py)

to (px, py) with pcolor

}

LCD_Erase() {

Draw rectangle from (XMIN, YMIN)

to (XMAX, YMAX) filled with

background bg_clr

}

```

# D. Comparator Interrupt Triggers Data Acquisition

- CMP Interrupt Handler

for (n=0; n<NS; n++) {

r = ADC->Result;

y = scale(r);

LCD\_Plot(x++, y, tr\_clr);

}

- Thread

...

// Detector/Synchronizer

if (Erase\_Pressed)

LCD\_Erase();

...

- Trigger

- Synchronize: Comparator detects trigger, requests interrupt

- Schedule: Interrupt System

- Dispatch: Interrupt System

- Erase

- Synchronize: Polling/analysis test in thread

- Schedule: SW test

- Dispatch: Subroutine call

Problem #1 with Approach D

```

CMP Interrupt Handler

for (n=0; n<NS; n++) {

r = ADC->Result;

y = scale(r);

LCD_Plot(x++, y, tr_clr);

}

```

```

Thread

...

// Detector/Synchronizer

if (Erase_Pressed)

LCD_Erase();

...

```

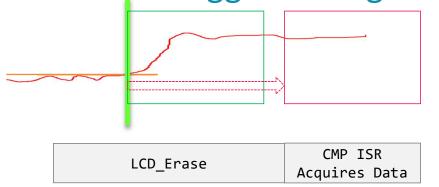

- What if scope is triggered during an erase?

- Start to erase screen, get partway through

- Plot trace

- Erase rest of screen, maybe erasing part of new trace just plotted

- Observation

- LCD\_Erase is not executed atomically, can run concurrently with CMP ISR

- Should LCD\_Erase be executed atomically?

### E.1. Handle Trigger During Erase

- Solution (?) 1.0

- Don't continue erasing after interrupt?

- May leave old unerased trace in part of screen

- Not clear yet how to make LCD Erase() give up partway through.

- Solution (?) 1.1

- Disable interrupts (or just comparator interrupt) during LCD\_Erase?

- Long synchronization delay possible from trigger condition to CMP ISR execution

# Thread ... // Detector/Synchronizer if (Erase\_Pressed) save CMP interrupt enabled state; disable CMP interrupt; LCD\_Erase(); restore CMP interrupt enabled state ...

### E.1. Handle Trigger During Erase

```

CMP Interrupt Handler

for (n=0; n<NS; n++) {

r = ADC->Result;

y = scale(r);

LCD_Plot(x++,y);

}

NewDAcqDone = 1

```

- Solution (?) 1.2

- Break screen into tiles

- Erase each tile atomically, allow interrupts (triggering) between tiles

- Don't finish erasing if triggered during erase.

- Interrupt handler sets flag, LCD Erase tests flag

- What about tiles that aren't erased? Similar to 1.0, but reduces trigger detection latency

- Solution(?) 1.3

- When ISR runs, acquire data but don't plot it yet.

- Need to save it, trigger other code to run and plot it.

- More items on the Sync and Comm To Do List

- More complex, will examine deferred plotting in design F

```

Thread

...

// Detector/Synchronizer

if (Erase_Pressed)

LCD_Erase();

...

void LCD_Erase(void) {

for each tile {

if (NewDAcqDone) {

NewDAcqDone = 0;

break; // exit for loop

}

save CMP interrupt enabled state;

disable CMP interrupt;

draw background color rect. for tile

restore CMP interrupt enabled state

}

```

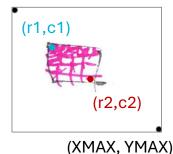

# Background for Problem #2: LCD Controller Interface (ST7789VI)

#### (XMIN, YMIN)

- MCU writes Command ID byte, then parameters (data bytes)

- **Received Command ID terminates previous** command, starts new command

- Received parameters interpreted based on most recent command

- Screen coordinates: columns (x) and rows (y)

- Draw rectangle between corners (c1,r1) and (c2,r2)

- Set first and last columns (CASET)

- Set first and last rows (RASET)

- Send pixels to fill in rectangle (RAMWR)

- Use LCD Plot and LCD Erase

| LCD_Plot(px, py, pcolor){     | LCD_Erase() {                         |

|-------------------------------|---------------------------------------|

| // Draw rectangle             | // Draw rectangle                     |

| LCD_Command(CASET, px, px)    | LCD_Command(CASET, XMIN, XMAX)        |

| LCD_Command(RASET, py, py)    | LCD_Command(RASET, YMIN, YMAX)        |

| LCD_Command(RAMWR, pcolor, 1) | n = (XMAX-XMIN + 1) * (YMAX-YMIN + 1) |

| }                             | LCD_Command(RAMWR, bg_color, n)       |

|                               | }                                     |

| Command ID                    | Parameters (data bytes) |    |    |    |    |     |

|-------------------------------|-------------------------|----|----|----|----|-----|

| (byte)                        | 1                       | 2  | 3  | 4  | 5  | ••• |

| Column Address<br>Set (CASET) | c1                      |    | c2 |    |    |     |

| Row Address Set<br>(RASET)    | r1                      |    | r2 |    |    |     |

| RAM Write<br>(RAMWR)          | d1                      | d2 | d3 | d4 | d5 |     |

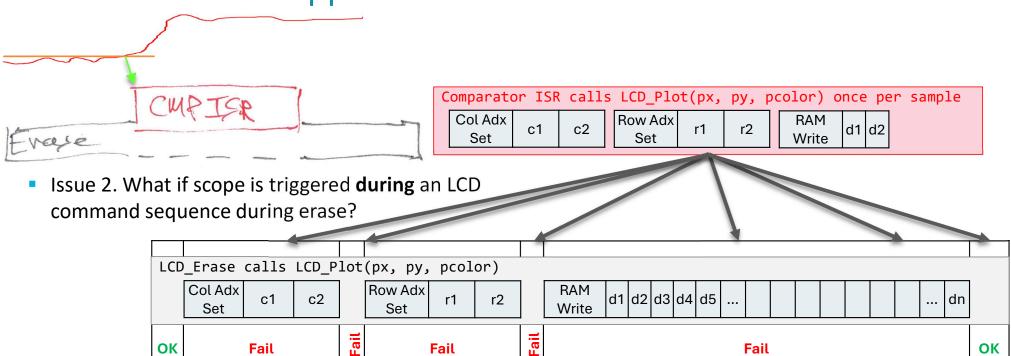

## Problem #2 with Approach D

- Result depends on when trigger occurs relative to LCD Erase's command sequence

- Before or after complete command sequence (CASET + data, RASET + data, RAMWR + data)? OK

- Before or after a command and its data: Fail

- Between a command and its data: Fail

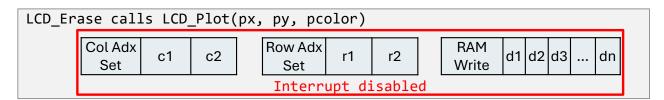

E.2. Trigger during LCD Command Sequence. Make LCD Controller

**Commands Atomic?**

- Solution (?) 2.1

- Don't allow triggering within LCD command sequences

- For each command + data sequence (CASET+data, RASET +data, RAMWR +data) within preemptable code (e.g. thread)...

- Disable comparator interrupt

- Send LCD command + data sequence

- Restore comparator interrupt state

- Display may still be corrupted by erasing newly plotted pixels

- As with 1.0, detection latency can be as long as erase time. Break screen into tiles? Still have problems

```

Thread

...

// Detector/Synchronizer

if (Erase_Pressed)

LCD_Erase();

...

void LCD_Erase_Atomic() {

save CMP interrupt enabled state;

disable CMP interrupt;

// Draw rectangle

LCD_Command(CASET, XMIN, XMAX)

LCD_Command(RASET, YMIN, YMAX)

n = (XMAX-XMIN + 1) * (YMAX-YMIN + 1)

LCD_Command(RAMWR, bg_color, n)

restore CMP interrupt enabled state

}

```

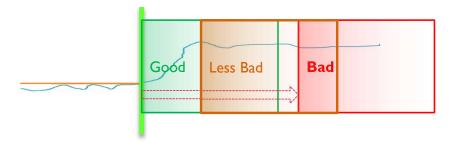

# Problems with Designs E.1, E.2

- LCD is shared by main thread and comparator interrupt handler

- Shared resource bugs for LCD\_Plot during LCD\_Erase

- High-level sharing (independent of LCD communication)

- Problem: want to erase everything but the new trace

- Critical sections cover up to entire screen

- LCD Erase: all pixels in each column

- LCD\_Plot: one pixel in each column

- Low-level sharing (LCD controller interface)

- Critical sections: Complete command sequence (CASET + data, RASET + data, RAMWR + data)

- Both designs prevent corruption of LCD communication and display contents

- But probably not good enough for scope

- Scope triggering is time-critical (real-time system)

- So try Solution(?) 1.3 despite complexity

- When ISR runs, acquire data but don't plot it yet.

- Need to save data, trigger other code to run and plot it => More for the Sync and Comm To Do List

# F: Hardware & OS Help: Comparator Interrupt, Deferred Plotting

- Trigger

- Synchronize: Comparator detects trigger, requests interrupt

- Schedule & Dispatch: Interrupt System

- Plot Data

- Synchronize: Test integrated w/ thread

- Schedule & Dispatch: Integrated w/ thread

- Erase

- Synchronize: Test integrated w/ thread

- Schedule & Dispatch: Integrated w/ thread

- What about retriggering while plotting?

- Synchronize by having CMP ISR do work if thread is done plotting data (NewDAcqDone)

- Consequences

- Skip disabling interrupts for safe LCD interfacing

- Skip dividing up LCD\_Erase for better responsiveness

- More delay to plot trace on LCD; only after all samples are acquired

```

volatile int NewDAcqDone=0;

CMP Interrupt Handler

if (NewDAcqDone==0) {

for (n=0; n<NS; n++) {

Buffer[n] = ADC->Result;

}

NewDAcqDone = 1;

}

```

```

Thread

```

```

if (NewDAcqDone) {

for (x=n=0; n<NS; n++) {

y = scale(Buffer[n]);

LCD_Plot(x++, y);

}

NewDAcqDone = 0

}

if (Erase_Pressed)

LCD_Erase();</pre>

```

- Trigger: Comparator Interrupt Handler

- Synchronize: Comparator detects trigger, requests interrupt

- Sample Data: Timer Interrupt Handler

- Synchronize: Timer requests interrupt

- Plot Data

- Synchronize: Integrated w/ thread

- Erase

- Synchronize: Integrated w/thread

- What about retriggering while plotting?

- Test NewDAcqDone in trigger detection (CMP) interrupt handler

- Consequences

- No need to disable interrupts for LCD safety or divide LCD Erase for responsiveness

- More delay to plot trace on LCD; only after all samples are acquired

```

volatile int NewDAcqDone=0;

// input sample number

volatile int n_is=0;

CMP Interrupt Handler

if (NewDAcqDone == 0) {

n is = 0

Start timer

```

```

ADC->Result;

if (n is == NS) {

Stop timer

NewDAcqDone = 1;

```

#### **Thread**

```

if (NewDAcaDone) {

for (x=n=0; n< NS; n++) {

y = scale(Buffer[n]);

LCD Plot(x++, y);

NewDAcqDone = 0

if (Erase Pressed)

LCD Erase();

```

## H: Sample Data with Timer-Driven DMA

- Trigger Detection

- Synchronize: Comparator detects trigger, requests interrupt

- Sample Data

- HW: DMA transfers from ADC to Buffer

- Plot Data

- Synchronize: Integrated with thread

- Erase

- Synchronize: Integrated with thread

- What about retriggering during plotting?

- Same as F, G

- Consequences

- Responsiveness from trigger condition to start of sampling is limited by interrupt latency

- In affordable systems, sample rate is limited by ADC

```

volatile int NewDAcqDone=0;

CMP Interrupt Handler

if (NewDAcqDone==0){

Start timer

}

```

NewDAcq

```

Stop timer

NewDAcqDone = 1;

```

```

Thread

...

if (NewDAcqDone) {

for (x=n=0; n<NS; n++) {

y = scale(Buffer[n]);

LCD_Plot(x++, y);

}

NewDAcqDone = 0

}

if (Erase_Pressed)

LCD_Erase();</pre>

```