#### 17:

# WaveGen: Loosening Timing Requirements, Interfering Less with Other Processing

**v**2

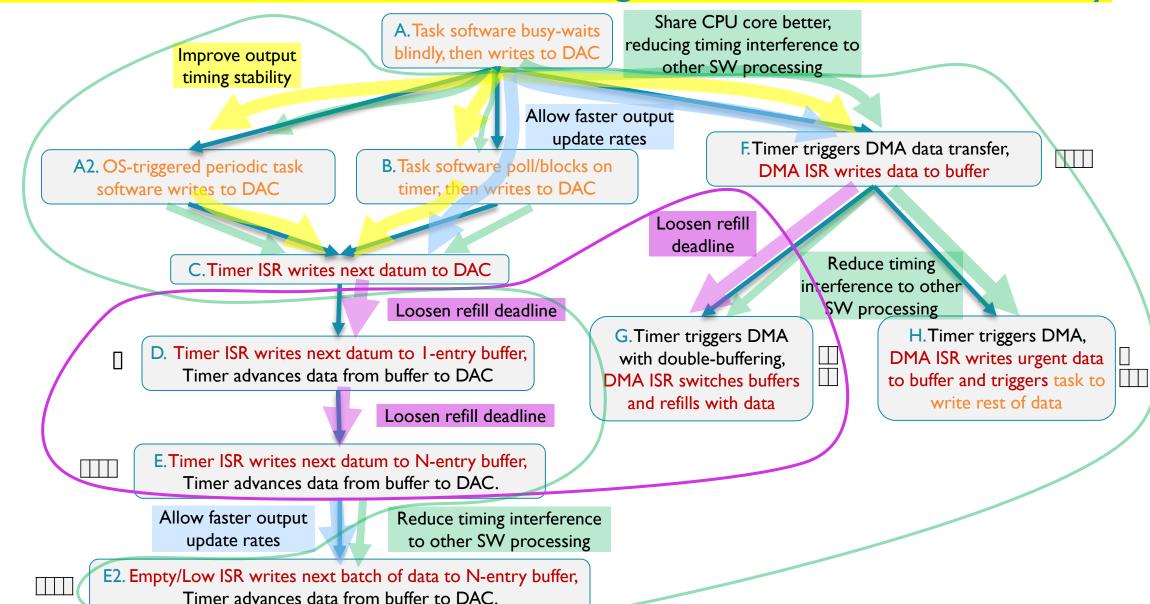

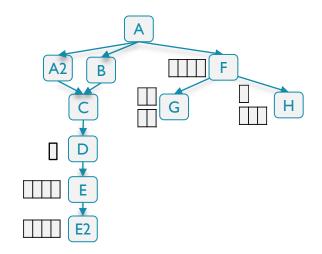

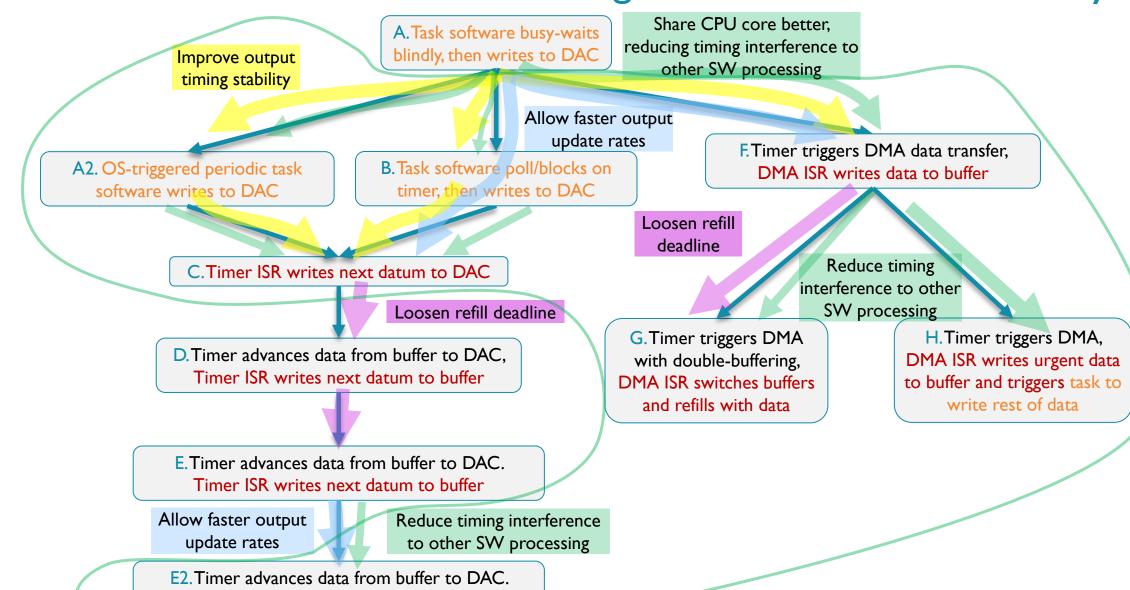

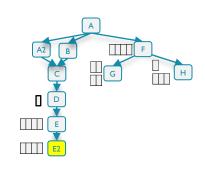

# Overview of Waveform Generator Design Evolution: What and Why

#### Detailed Overview of What and Why

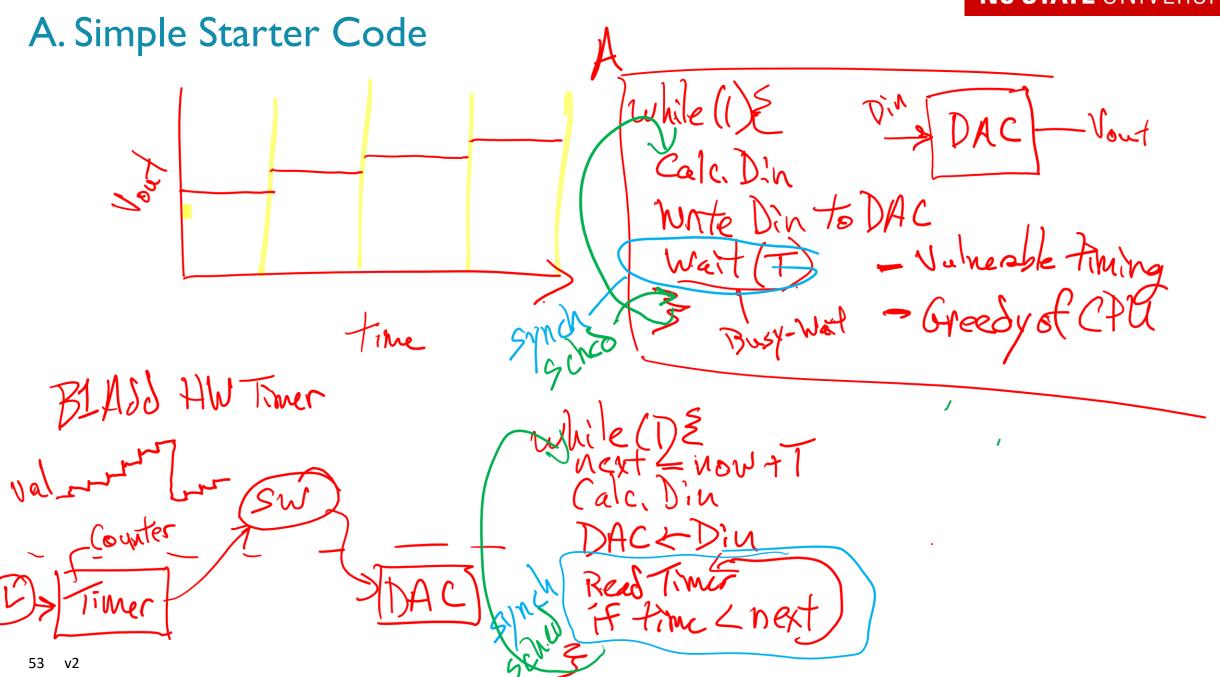

Output timing bad: Very unstable, vulnerable to other software (processes and handlers), timing errors accumulate. **Greedy**, doesn't share CPU.

And add QS with ticks from HW timer interrupts

> A2. OS-triggered periodic task software writes to DAC

Output timing better: Tolerates more interference, vulnerable to processes and handlers, errors don't accumulate. Shares CPU.

Tight deadline: T<sub>Samble</sub>

Output timing: Even better.

Vulnerable to preemption and blocking f<sub>samble</sub> times/sec

Fight deadline: T<sub>Samble</sub>

Put code in HW timer's ISR

Use N-deep DAC

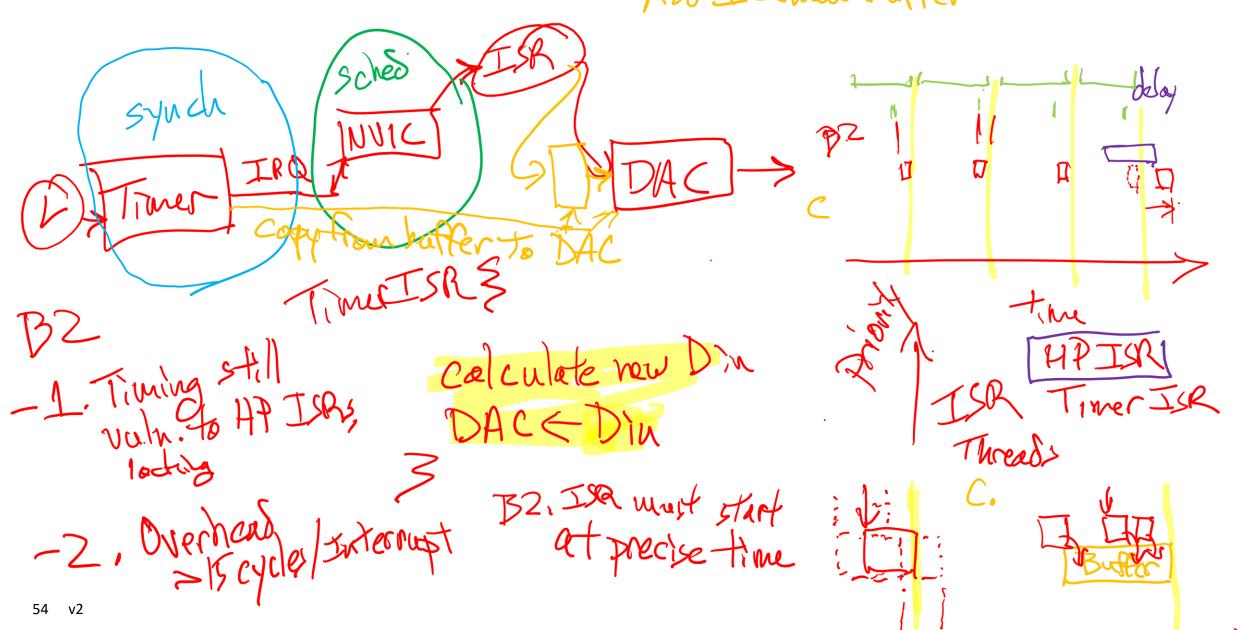

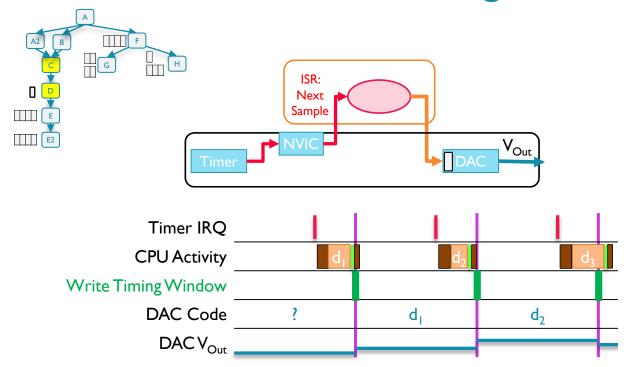

C.Timer ISR writes next data to DAC

Use 1-deep DAC input buffer

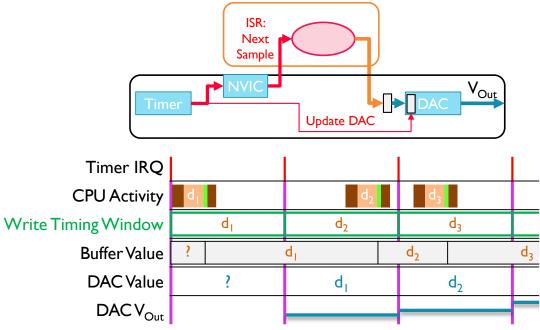

D. Timer ISR writes next datum to 1-entry buffer, Timer advances data from buffer to DAC

Deadline better: 2T<sub>Sample</sub> Interrupt overhead for each sample wastes CPU time.

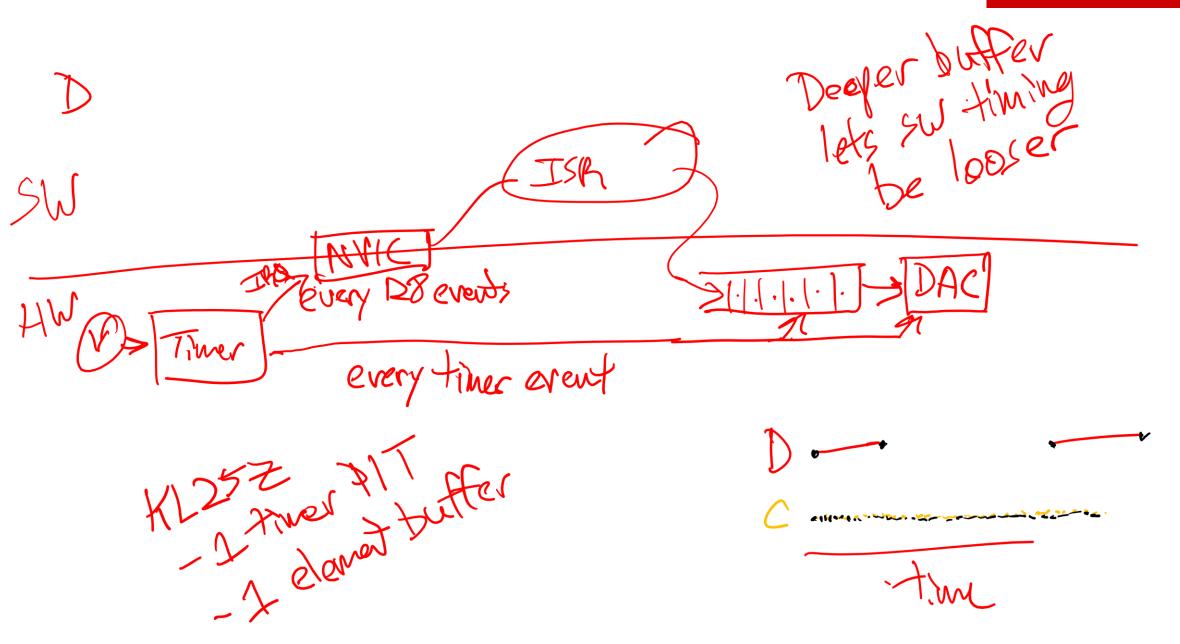

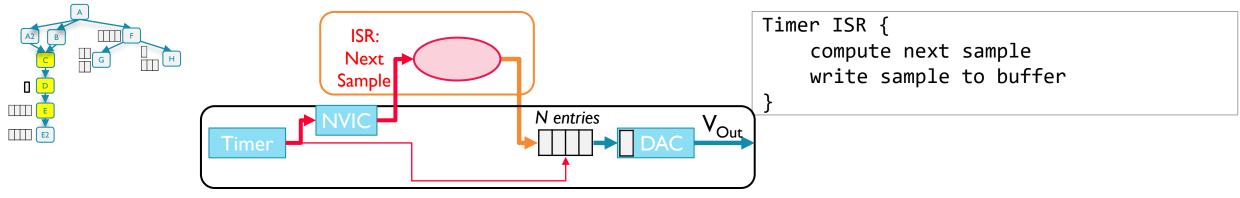

input buffer E. Timer ISR writes next datum to N-entry buffer,

Timer advances data from buffer to DAC.

Interrupt overhead for each sample wastes CPU time

Use low/empty ISR with N-deep DAC input buffer

E2. Empty/Low ISR writes next batch of data to N-entry buffer, Timer advances data from buffer to DAC.

A. Task software writes to DAC

Add HW timer (tracks time accurately

And access HW timer directly

B. Task software poll/blocks on timer, then writes to DAC

> Output timing better: Tolerates more interference, vulnerable to processes and handlers, errors don't accumulate. Greedy, doesn't

> > share CPU. Tight deadline: T<sub>Sample</sub>

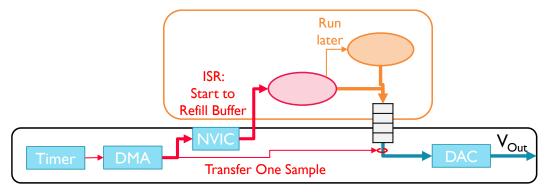

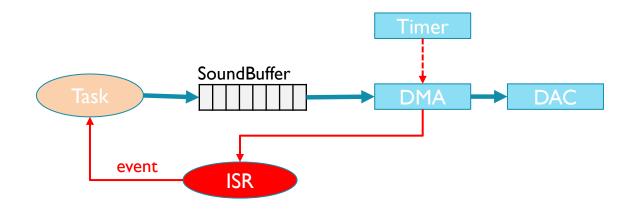

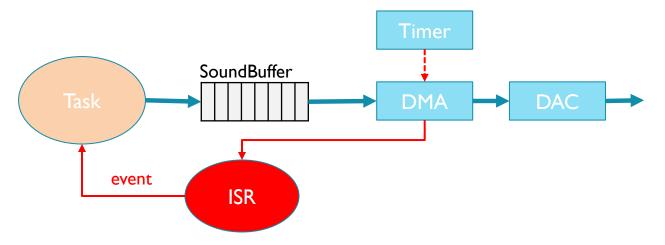

And add DMA with ISR. software buffer

F.Timer triggers DMA data transfer, DMA ISR writes data to buffer

1. Tight Deadline: ISR must write first new sample to buffer within T<sub>Sample</sub>

2. Long DMA ISR is delays other processing too much

Split into double-buffer to ease first sample's deadline and cuts ISR duration in half.

G. Timer triggers DMA with double-buffering, DMA ISR switches buffers and refills with data

Move non-urgent work to task

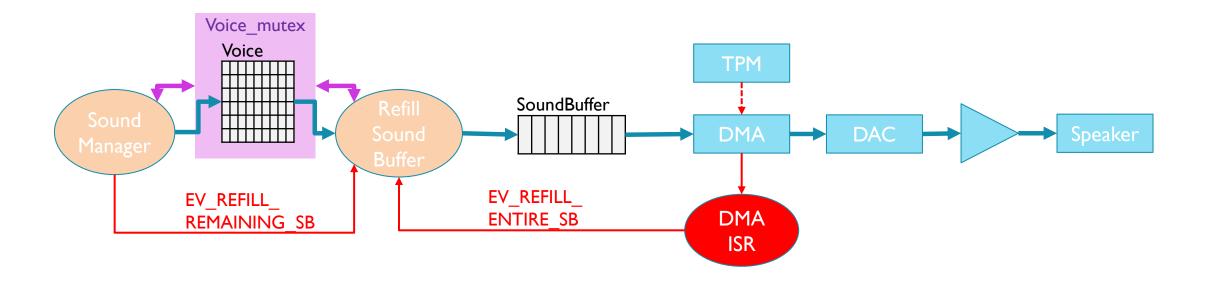

H. Timer triggers DMA, DMA ISR writes urgent data to buffer and triggers task to write rest of data

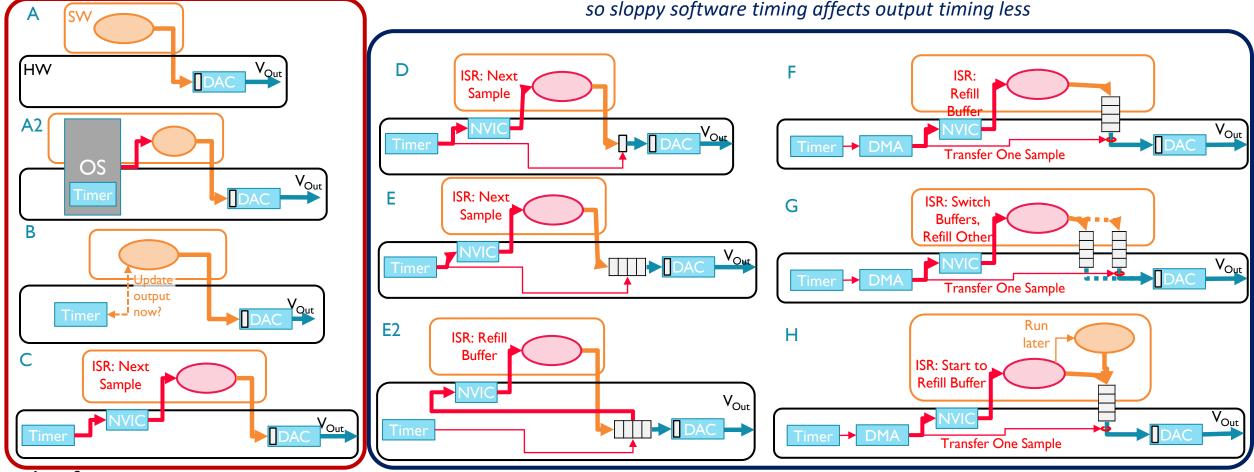

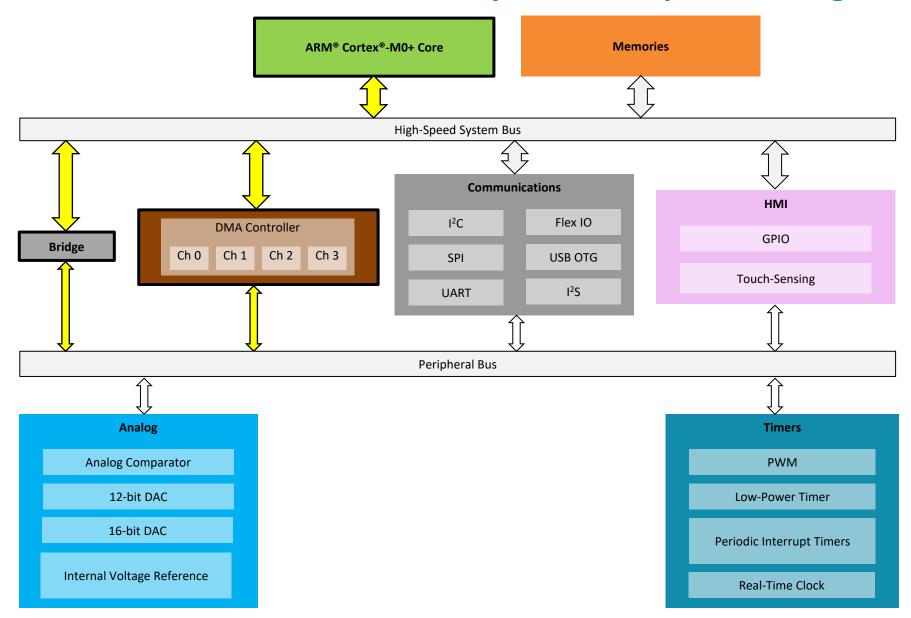

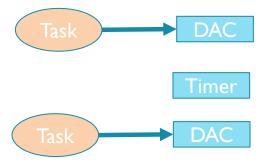

# Software and Hardware Components in Design Evolution

**General Trend**: Move operations which need synchronization (update output, compute new value) from **software** to **hardware** to improve stability, performance

**Synchronous Output: Software write** to hardware **changes output**, so sloppy timing

Asynchronous Output: Output is updated by hardware, so it is decoupled from (asynchronous with) software execution, so sloppy software timing affects output timing less

## **LOOSENING DEADLINES**

#### Reminder of Recent Designs C & D

- C.Timer ISR

- Output update is still synchronous with software, since write in ISR updates DAC

- Better timing stability because ISR has priority and can preempt other code

- D.Timer triggers DAC to copy data from single element buffer

- Output update is now asynchronous with software, since timer signal updates DAC

- Much better timing stability because of wider write timing window (T<sub>sample</sub>), so easier to make software meet it

- Improves timing stability by loosening deadlines. Can extend this approach.

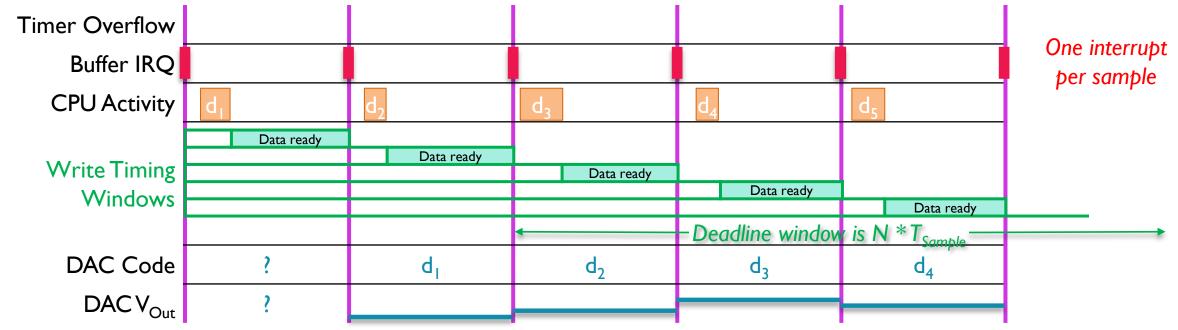

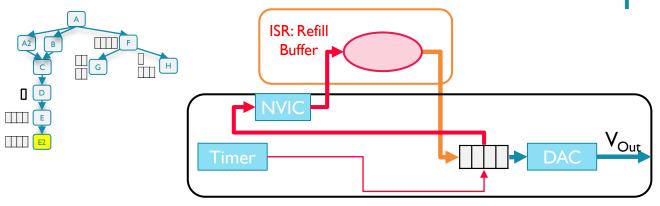

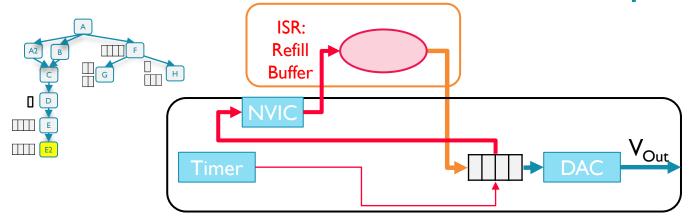

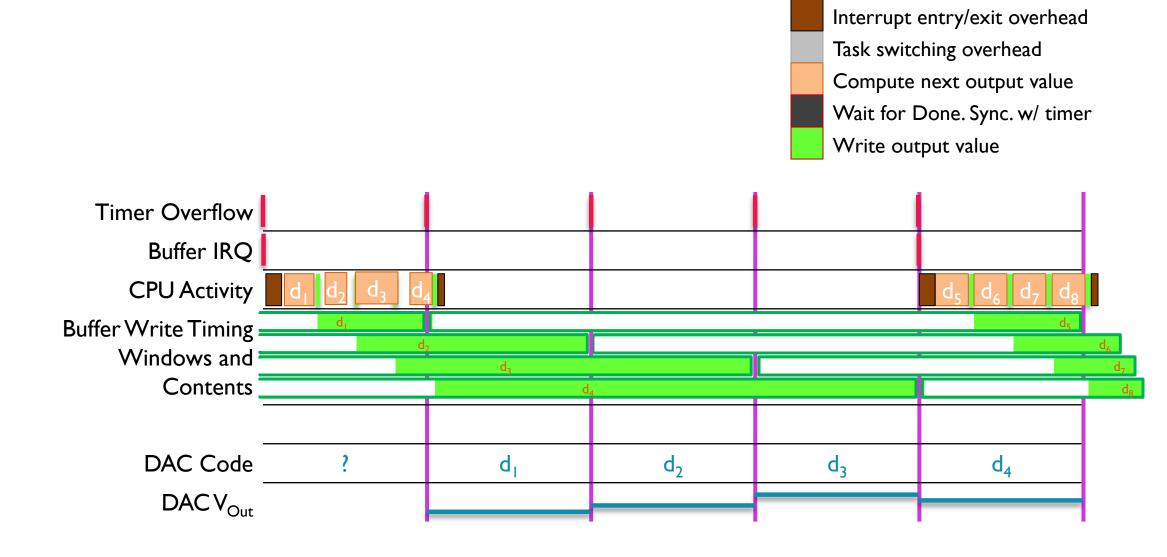

# E.Add N-Item Buffer for DAC, Interrupt per Sample

- Extend buffer to multiple-entry queue, aka FIFO (first-in, first-out)

- Note: is part of peripheral hardware design. More likely to be available in higher-performance peripherals.

# Concepts: Buffering Data for an Asynchronous Output

- Is example of Asynchronous I/O

- Output data samples are generated when ISR runs

- DAC output changes when timer signal triggers update

- Async I/O requires storing data temporarily

- From producer generating the data (timer ISR)

- Until consumer reads the data for use (timer overflow signal triggers DAC)

- Inherent limitations of buffering

- Delays when data reaches output signal

- Buffering and requires pre-computation, so not possible if outputs depend on future unknown data (e.g. control system)

- Producer, consumer must synchronize buffer accesses

- Producer: don't add data if buffer is full

- Consumer: don't read data if buffer is empty

- Both: don't interfere with each other's buffer accesses.

- Some buffer implementations have critical sections of code which must be protected

- Need deeper buffers as producer, consumer timing characteristics diverge

- Timing tolerance mismatches:

- Producer runs once per 100 us, but within 100 us window, so has timing jitter of up to 100 us

- Output allows much less timing jitter (e.g. 10 us)

- Peak data rate mismatch:

- Producer's maximum rate > consumer's maximum rate

- Timing uncertainty from blocking and preemption:

- Consumer may not get run enough for unknown range of times (jitter for task completion time)

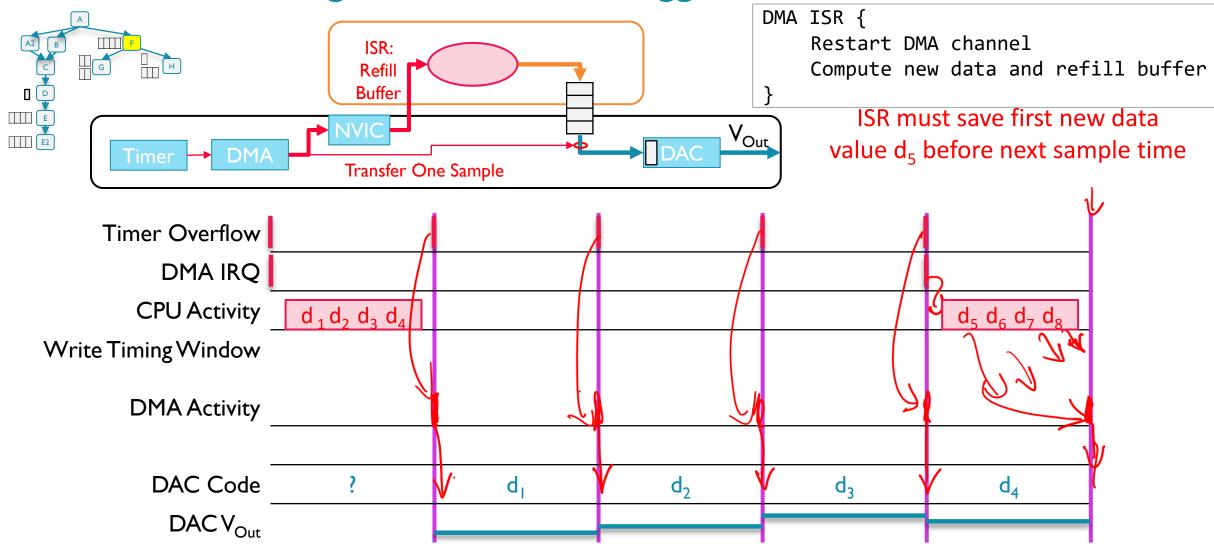

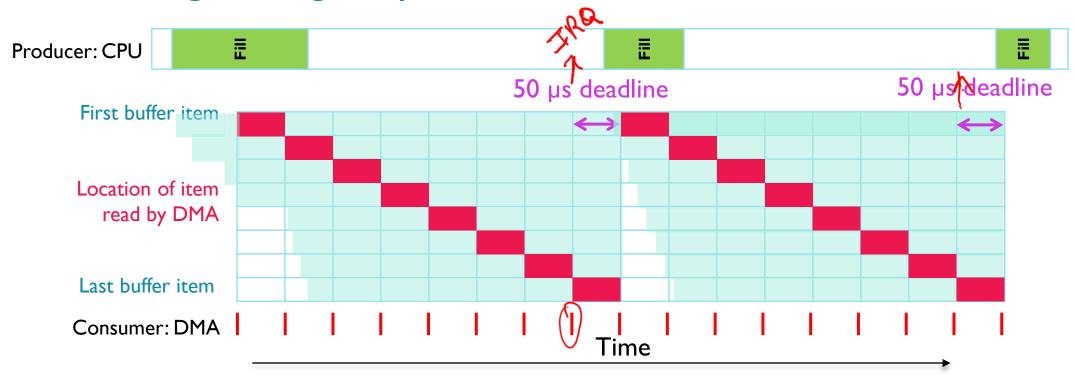

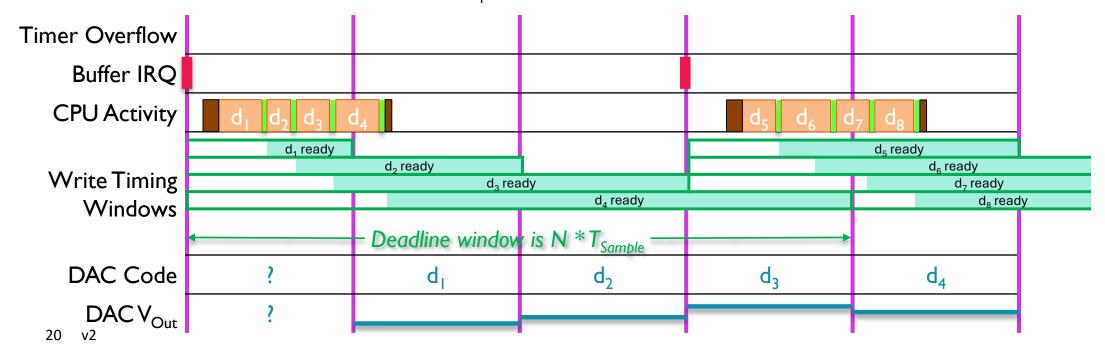

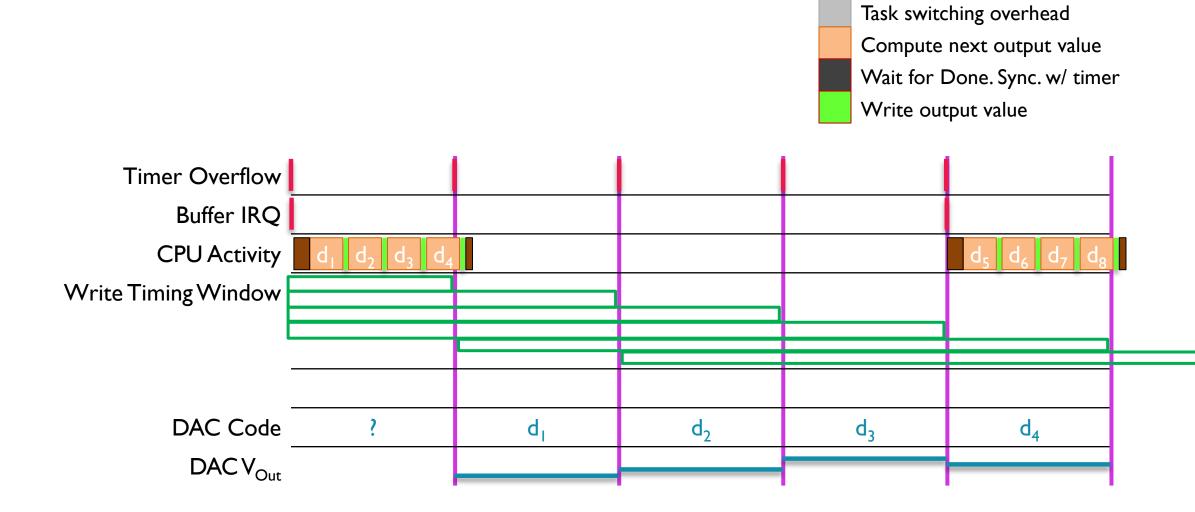

Reminder of Design F. Use Timer-Triggered DMA to Transfer Data

#### Examining Timing Requirements for Buffer Refill

- Behavior

- CPU (producer) adds data to fill buffer

- DMA (consumer) reads data items

- Data item in buffer is not needed (old, stale) after being read by consumer

- Producer (Thread\_Refill\_Sound\_Buffer) must stay ahead of consumer (DMA controller)

- Behavior after DMA transfers last data item

- DMA generates interrupt request

- ISR contains producer

- Must refill 1<sup>st</sup> buffer entry within T<sub>Sample</sub>, 2<sup>nd</sup> entry within 2\*T<sub>Sample</sub>, etc.

- First deadline may be too tight to meet easily

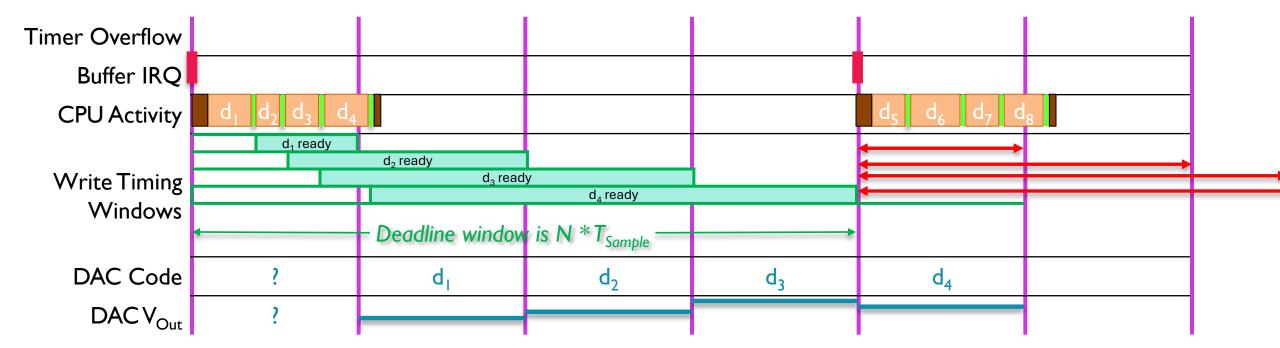

# Loosening Timing Requirements with Double-Buffering

- Use two buffers, each half-size (N = 4 entries)

- Initialization

- Start filling buffer 0

- Can start playing buffer 0 after it has ≥1 sample

- After buffer 0 is filled, start filling buffer 1

- Operation: After playing last sample from buffer 0,

- Switch to playing buffer I

- Start refilling buffer 0

- Generalization

- After playing last sample from buffer x, switch to playing buffer y, start filling buffer x

- Deadlines

- Now have two deadlines, one per buffer ⊗

- Much looser deadlines: extended to from T<sub>Sample</sub> to  $(N+I)*T_{Sample}$

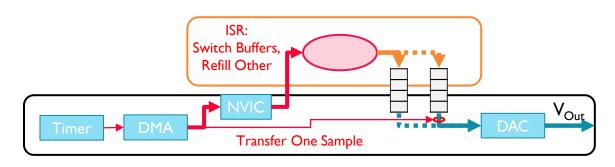

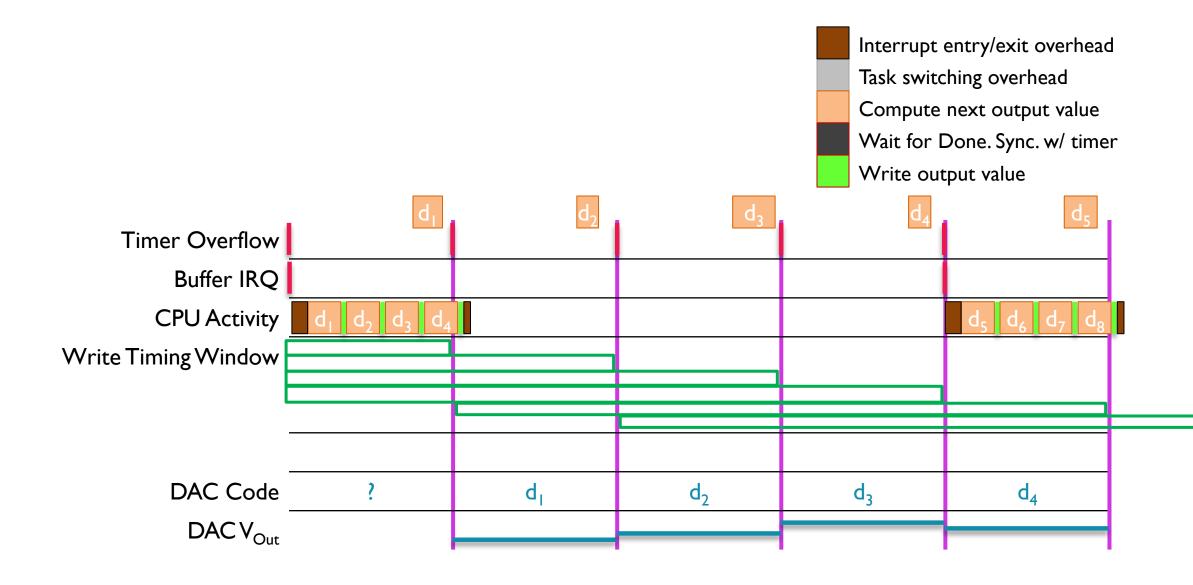

#### G. DMA with Double Buffering

```

int rbn = 0; // reader's buffer number

uint16_t buffer[2][1024];

Initialization code prefills buffer[0]

DMA IRQ Handler {

old_bn = rbn;

rbn = 1 - rbn; // Switch buffers

Restart DMA with buffer[rbn]

Refill buffer[old_bn]

}

```

#### G. DMA with Double Buffer

# REDUCE TIMING INTERFERENCE FOR OTHER SW PROCESSING (SHARE CPU BETTER)

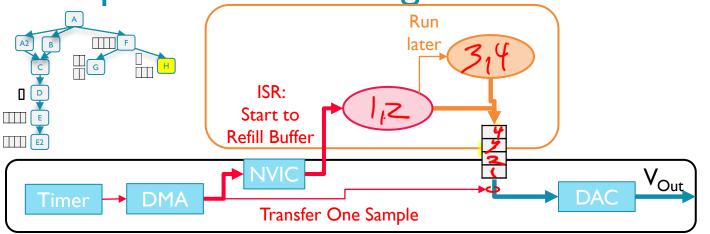

# Overview of Waveform Generator Design Evolution: What and Why

Low/Empty ISR writes next batch of data to buffer

#### Detailed Overview of What and Why

Output timing bad: Very unstable, vulnerable to other software (processes and handlers), timing errors accumulate. **Greedy**, doesn't share CPU.

> And add QS with ticks from HW timer interrupts

> > A2. OS-triggered periodic task software writes to DAC

Output timing better: Tolerates more interference, vulnerable to processes and handlers, errors don't accumulate. Shares CPU.

Tight deadline: T<sub>Samble</sub>

Output timing: Even better. Vulnerable to other ISRs and interrupt locking  $f_{samble}$  times per second

Tight deadline: T<sub>Samble</sub>

Put code in HW timer's ISR

Output timing better: Tolerates more

interference, vulnerable to processes and handlers, errors don't accumulate. Greedy, doesn't

share CPU. Tight deadline: T<sub>Sample</sub> C.Timer ISR writes next data to DAC

A. Task software writes to DAC

Add HW timer (tracks time accurately

And access HW timer directly

B. Task software poll/blocks on timer, then writes to DAC

And add DMA with ISR, software buffer

F.Timer triggers DMA data transfer, DMA ISR writes data to buffer

1. Tight Deadline: ISR must write first new sample to buffer within T<sub>sample</sub>

2. Long DMA ISR is delays other processing too much

Use 1-deep DAC input buffer

D. Timer advances data from buffer to DAC. Timer ISR writes next data to buffer

Deadline better: 2T<sub>Sample</sub> Interrupt overhead for each sample wastes CPU time.

Use N-deep DAC input buffer with low/empty ISR

E. Timer advances data from buffer to DAC. Timer ISR writes next data to buffer

Interrupt overhead for each sample wastes CPU time

Add N-deep DAC input buffer with low/empty ISR

E2. Timer advances data from buffer to DAC. Low/Empty ISR writes next batch of data to buffer Split into double-by fer to ease first sample's dead ne and cuts ISR duration in half.

G. Timer triggers DMA with double-buffering, **DMA ISR** switches buffers and refills with data

Move non-urgent work to task

H. Timer triggers DMA, DMA ISR writes urgent data to buffer and triggers task to write rest of data

E2. DAC Buffer Generates Interrupt Only When Buffer is Empty

```

DAC Buffer ISR {

while (buffer not full) {

compute next sample

write sample to buffer

}

}

```

- Reduce timing interference to other processing by generating fewer interrupts. Burst/batch processing

- Divides number of interrupts by buffer size

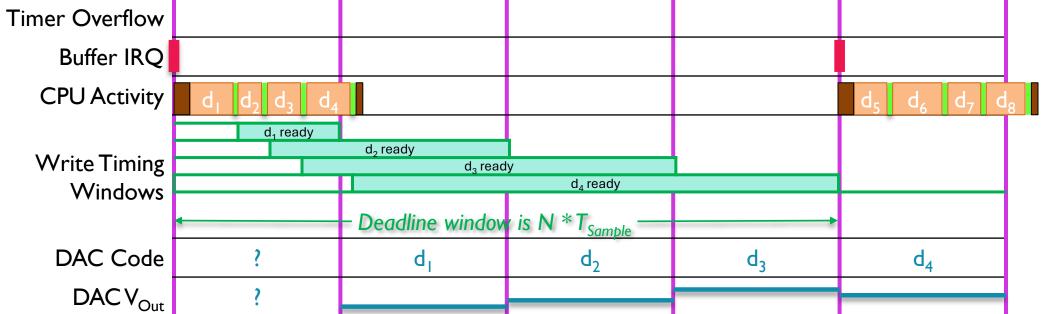

# Tighter Timing Requirements for Refilling Buffer

- First sample has deadline of T<sub>Sample</sub>

- Second sample has deadline of 2\*T<sub>Sample</sub>

- Third sample has deadline of 3\*T<sub>Sample</sub>

- Deadline is shorter than window because interrupt occurs late when last sample is read

- Same as problem with DMA design F (solved F with double buffering in G)

- Can DAC Buffer give us an early warning interrupt before the buffer is full?

# E3. DAC Buffer Generates Interrupt when Buffer is 3/4 Empty

DAC Buffer ISR {

while (buffer not full) {

compute next sample

write sample to buffer

}

}

- Interrupt occurs  $(N/4)*T_{sample}$  earlier

- Deadline to refill first entry is now (I+N/4)\*T<sub>Sample</sub>

- Make sure that none of the last N/4 samples are overwritten

- Must synchronize within the ISR to the DMA. Put on Sync To Do List

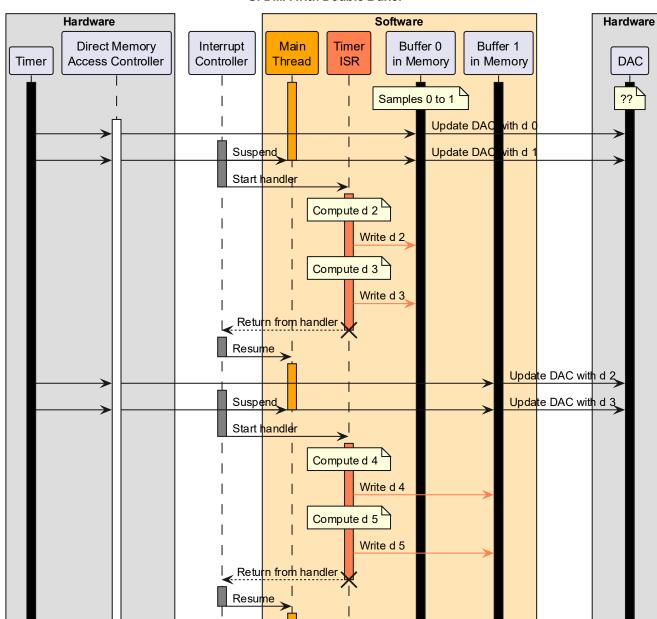

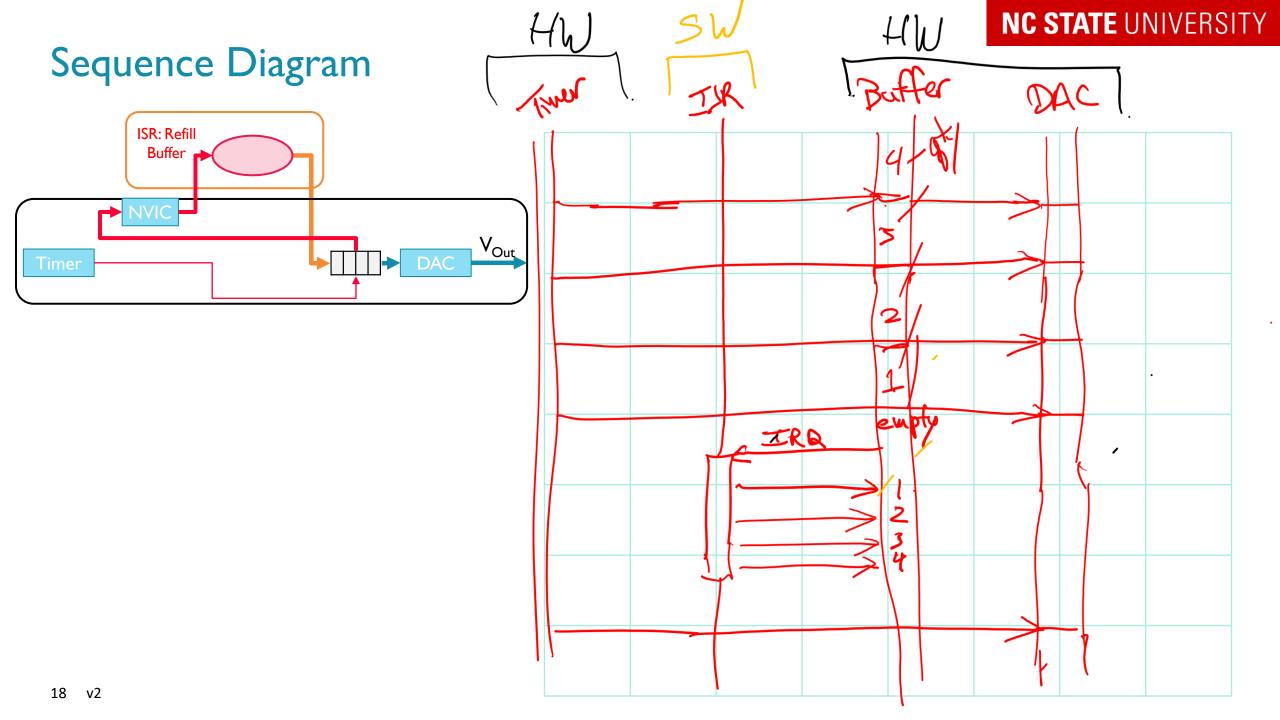

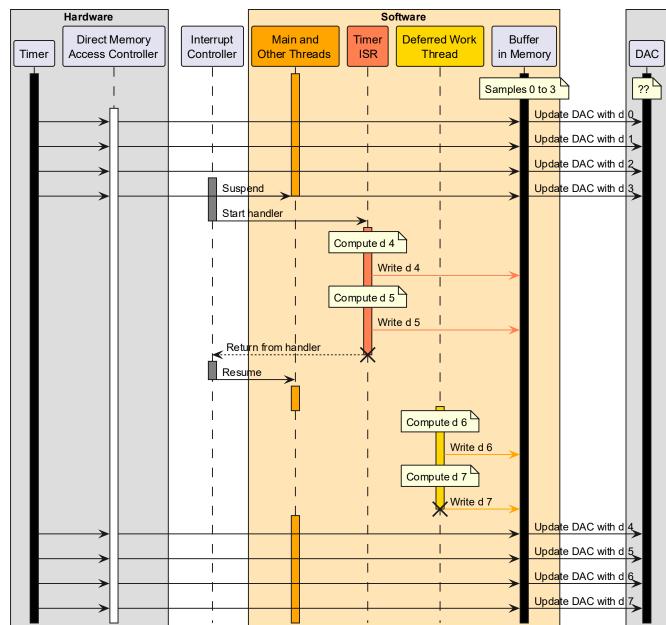

H. Split Work into Urgent and Deferred

```

ISR {

do urgent work now

request deferred proc'g for rest of work

}

thread_Deferred_Work {

do remaining work

}

```

- When refill buffer ISR runs, it can delay ISRs (with same or lower priority) and all threads

- Want to reduce time spent in ISR to improve responsiveness for other software processing

- Observation: Don't need to refill entire buffer in ISR

- Refilling first sample in buffer is highest urgency

- Lower urgency for second, even lower for third...

- Procrastinate!

- Change ISR to refill N most urgent samples (e.g. 1 & 2), and request thread to finish the work

- Defer remaining BUFSIZE N samples (e.g. 3 & 4) for thread to refill

- Depends on some form of thread scheduler to run the refill thread

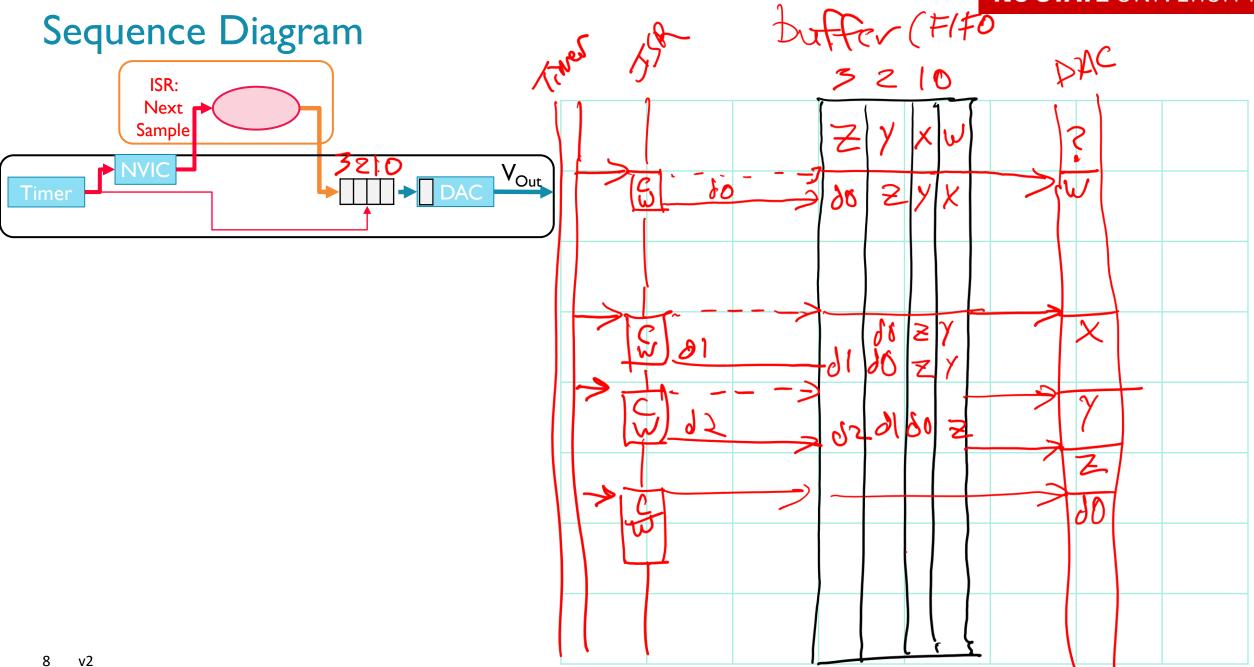

# Sequence Diagram

#### H. DMA with Deferred Work (Arbitrary Scheduler)

# **SUMMARY**

# Implementation Analysis

- A2. OS runs task periodically, task writes to DAC

- B. Task software poll/blocks on timer, then writes to DAC

- C. Timer ISR writes data to DAC

- D. Timer advances buffer data to DAC, Timer ISR writes next data to buffer

- E.Timer advances buffer data to DAC. Timer ISR writes data to buffer

- E2. Timer advances buffer data to DAC. Low/Empty ISR writes next batch of data to buffer

- F.Timer triggers DMA data transfer, DMA ISR writes next batch of data to buffer

- G. Timer triggers DMA transfer, DMA ISR switches buffers and writes next batch of data to previous buffer

- H. Timer triggers DMA transfer, DMA ISR writes urgent data to buffer, triggers task. Task writes rest of data batch

# Implementation Comparison

| Issue                                                                      | A. SW -><br>DAC                     | B. SW Polls<br>Timer | C. Timer ISR             | D. Add<br>single DAC<br>buffer | E. Multi-<br>Entry DAC<br>Buffer | F. DMA<br>Transfer | G. Double<br>Buffering | H. Defer<br>Some W |

|----------------------------------------------------------------------------|-------------------------------------|----------------------|--------------------------|--------------------------------|----------------------------------|--------------------|------------------------|--------------------|

| CPU Sharing                                                                | Greedy                              | Greedy               | Good                     |                                |                                  |                    |                        |                    |

| Time Tracking                                                              | SW fixed<br>busy-wait<br>delay loop | SW polls HW<br>timer | HW timer                 |                                |                                  |                    |                        |                    |

| Resynch on next sample?                                                    | No                                  | Yes                  | Yes                      |                                |                                  |                    |                        |                    |

| Vulnerable to other tasks                                                  | Yes                                 | Yes                  | No                       |                                |                                  |                    |                        |                    |

| Vulnerable to ISRs, Handlers                                               | Yes                                 | Yes                  | Only higher-<br>priority |                                |                                  |                    |                        |                    |

| Width of timing window                                                     | $T_{CPU}$                           | $T_CPU$              | $T_CPU$                  | $T_{sample}$                   |                                  |                    |                        |                    |

| Relative Deadline: from notification until updating first sample in buffer |                                     |                      |                          | T <sub>sample</sub>            |                                  |                    |                        |                    |

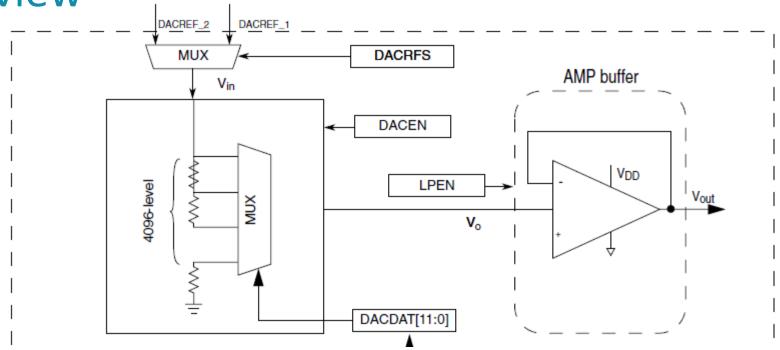

#### **DIGITAL TO ANALOG CONVERTER**

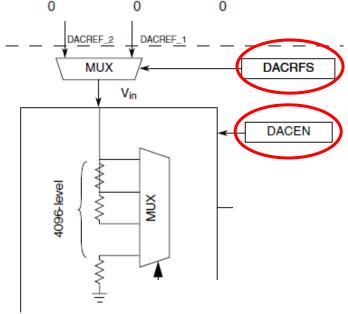

**DAC Overview**

- Load DACDAT with 12-bit data N

- MUX selects a node from resistor divider network to create  $V_0 = (N+1)*V_{in}/2^{12}$

- V<sub>o</sub> is buffered by output amplifier to create V<sub>out</sub>

- $V_0 = V_{out}$  but  $V_0$  is high impedance can't drive much of a load, so need to buffer it

#### **DAC** Registers

#### DAC memory map

| Absolute<br>address<br>(hex) | Register name                       | Width<br>(in bits) | Access | Reset value | Section/<br>page |

|------------------------------|-------------------------------------|--------------------|--------|-------------|------------------|

| 4003_F000                    | DAC Data Low Register (DAC0_DAT0L)  | 8                  | R/W    | 00h         | 30.4.1/531       |

| 4003_F001                    | DAC Data High Register (DAC0_DAT0H) |                    | R/W    | 00h         | 30.4.2/532       |

| 4003_F002                    | DAC Data Low Register (DAC0_DAT1L)  | 8                  | R/W    | 00h         | 30.4.1/531       |

| 4003_F003                    | DAC Data High Register (DAC0_DAT1H) | 8                  | R/W    | 00h         | 30.4.2/532       |

| 4003_F020                    | DAC Status Register (DAC0_SR)       | 8                  | R      | 02h         | 30.4.3/532       |

| 4003_F021                    | DAC Control Register (DAC0_C0)      | 8                  | R/W    | 00h         | 30.4.4/533       |

| 4003_F022                    | DAC Control Register 1 (DAC0_C1)    | 8                  | R/W    | 00h         | 30.4.5/534       |

| 4003_F023                    | DAC Control Register 2 (DAC0_C2)    | 8                  | R/W    | 0Fh         | 30.4.6/534       |

- This peripheral's registers are only eight bits long (legacy peripheral).

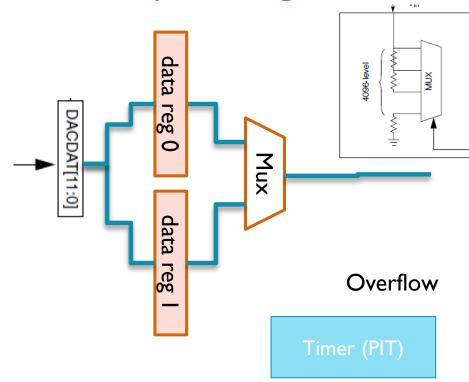

- DATA[11:0] stored in two registers

- DATA0: Low byte [7:0] in DACx\_DATnL

- DATA1: High nibble [11:0] in DACx\_DATnH

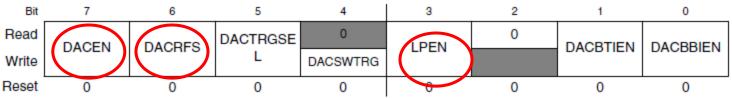

#### DAC Control Register 0: DACx C0

- DACEN DAC Enabled when 1

- DACRFS DAC reference voltage select

- 0: DACREF 1. Connected to VREFH

- 1: DACREF\_2. Connected to VDDA

- LPEN low-power mode

- 0: High-speed mode. Fast (15 us settling) time) but uses more power (up to 900 uA supply current)

- 1: Low-power mode. Slow (100 us settling time) but more powerefficient (up to 250 uA supply current)

- Additional control registers used for buffered mode

#### **DAC Operating Modes**

Normal

DACEN

LPEN

- Value written to DACDAT is converted to voltage immediately

- Buffered mode eases timing requirements

Buffered

- Value written to DACDAT is stored in data buffer for later conversion

- Next data item is sent to DAC when triggered

- Software Trigger write to DACSWTRG field in DACx\_C0

- Hardware Trigger from PIT timer peripheral

- Normal Mode: Circular buffer

- One-time Scan Mode: Pointer advances, stops at end of buffer

- Status flags in DACx\_SR

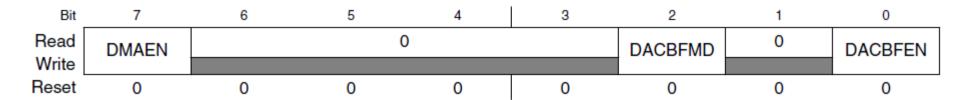

#### DAC Control Register 1: DACx C1

- DACBFEN

- 0: Disable buffer mode

- 1: Enable buffer mode

- DACBFMD Buffer mode select

- 0: Normal mode (circular buffer)

- 1: One-time scan mode

# Direct Memory Access (DMA) Controller

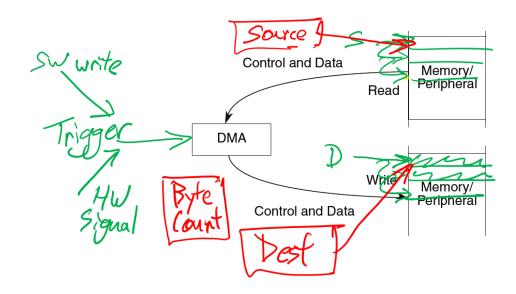

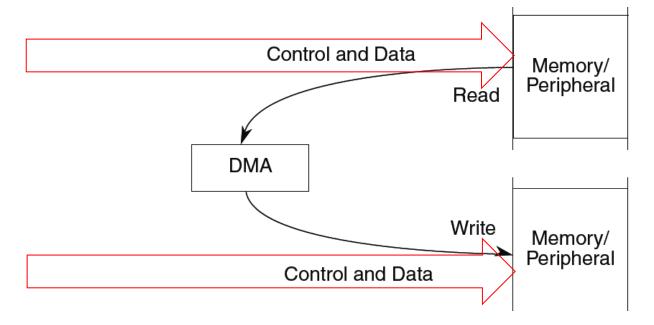

# DMA Can Read and Write Memory and Peripheral Registers

## **Basic Concepts**

- Memory copy machine built from hardware

- Reads data from source, writes it to destination

- Can eliminate ISRs which just copy data (e.g. copy ADC results into buffer)

- Key configurable options

- What event starts a transfer: software or hardware triggers

- Source and destination addresses, which can be fixed or change (e.g. increment, decrement)

- Number of data items to copy

- Size of data item (1, 2, 4 bytes)

- More features too: chaining, error handling...

- Sequence of operations

- Initialization: Configure controller

- Transfer: Data is copied

- Termination: Channel indicates transfer has completed (status flag, interrupt request, DMA request)

|   | Address            | Modification | Data Transfer Behavior                                                 |  |  |

|---|--------------------|--------------|------------------------------------------------------------------------|--|--|

|   | Source Destination |              | Data Transfer Bellavior                                                |  |  |

| • | fixed              | fixed        | Write value from fixed source location into fixed destination location |  |  |

|   | changes            | changes      | Copy values from source array to destination array                     |  |  |

|   | fixed              | changes      | Write value from fixed source location into array                      |  |  |

|   | changes            | fixed        | Write array contents to fixed destination location                     |  |  |

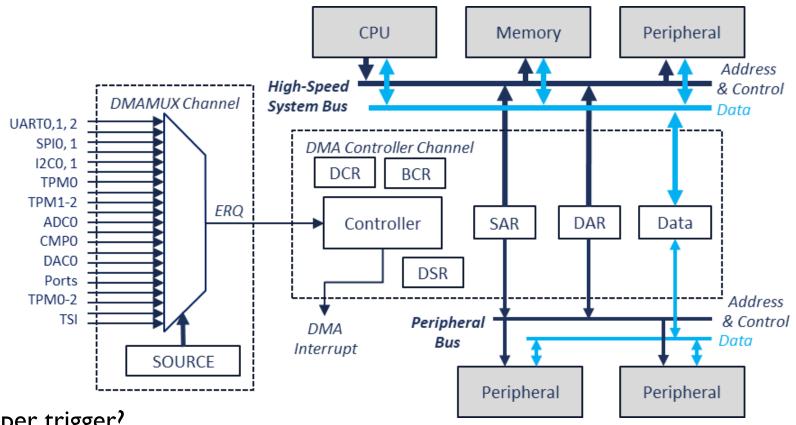

#### **DMA** Controller Details

- 4 independent channels

- Channel 0 has highest priority

- 8-, 16- or 32-bit transfers,

- Data size can differ between source and destination

- Circular/ring buffer support

- "Address Modulo:" address wraps around at end of buffer

- Buffer sizes from 64 B to 256 kB (2<sup>N</sup>)

- DMA MUX peripheral selects hardware signal for triggering

- How many data items are transferred per trigger?

- One: "Cycle stealing"

- All items: grabs bus

- Hardware acknowledge/done signal

# Address Registers

These registers determine from where the DMA will read its data, and to where it will write that data

- DMA\_SARn

- Source address register,

- Valid values 0 to 0x000f ffff

- DMA\_DARn

- Destination address register

- Valid values 0 to 0x000f ffff

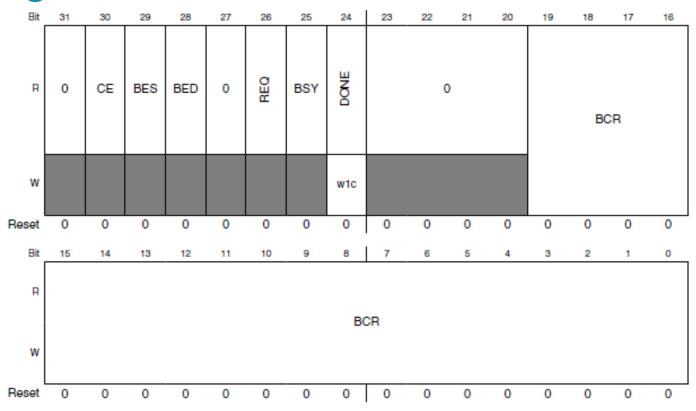

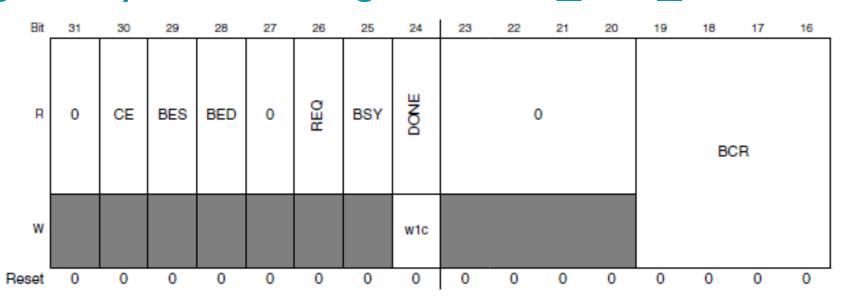

### Byte Count Register

- BCR: Bytes remaining to transfer

- Decremented by 1, 2 or 4 after completing write (determined by destination data size)

### Status Register/Byte Count Register DMA\_DSR\_BCRn

- Status flags: I indicates error

- CE: Configuration error

- BES: Bus error on source

- BED: Bus error on destination

- REQ:A transfer request is pending (more transfers to perform)

- BSY: DMA channel is busy

- DONE: Channel transfers have completed or an error occurred. Clear this bit in an ISR.

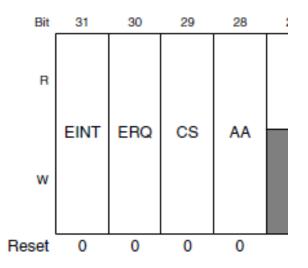

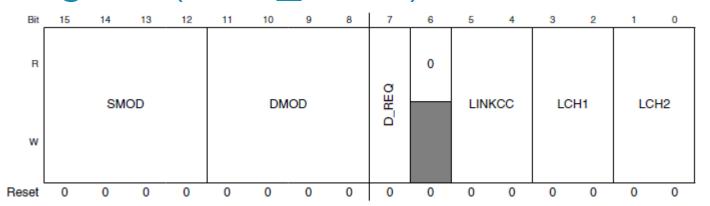

## DMA Control Register (DMA\_DCRn)

- EINT: Enable interrupt on transfer completion

- ERQ: Enable peripheral request to start transfer

- CS: Cycle steal

- 0: Greedy DMA makes continuous transfers until BCR == 0

- I: DMA shares bus, performs only one transfer per request

- AA: Autoalign

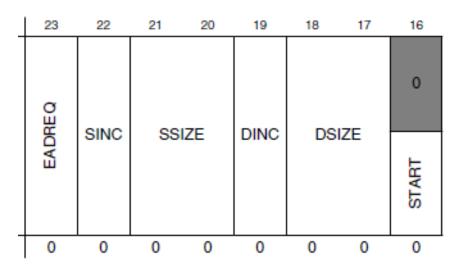

## DMA Control Register (DMA DCRn)

- EADRQ Enable asynchronous DMA requests when SSIZE/DSIZE Source/Destination data size. MCU is in Stop mode

- SINC/DINC Increment SAR/DAR by 1,2 or 4 based on size of data

- - Don't need to match controller will perform extra reads or writes as needed (e.g. read one word, write two bytes).

- 00: longword (32 bits)

- 01: byte (8 bits)

- 10: word (16 bits)

- START Write I to start transfer

## DMA Control Register (DMA\_DCRn)

- SMOD, DMOD Source/Destination address modulo

- When non-zero, supports circular data buffer address wraps around after 2<sup>n+3</sup> bytes (16 bytes to 64 kilobytes)

- When zero, circular buffer is disabled

- D\_REQ: If I, then when BCR reaches zero, channel will clear ERQ bit, preventing further hardware triggers of channel

- LINKCC: Enables this channel to trigger another channel

- 00: Disabled

- 01:Two stages:

- Link to channel LCH1 after each cycle-steal transfer

- Link to channel LCH2 after BCR reaches 0

- 10: Link to channel LCH1 after each cycle-steal transfer

- II: Link to channel LCHI after BCR reaches 0

- LCH1, LCH2: Values 00 to 11 specify linked DMA channel (0 to 3)

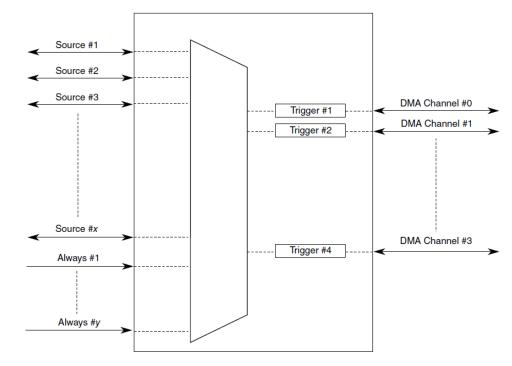

## Trigger Sources

- A variety of peripherals can trigger

DMA activity

- Trigger sources are chip-specific, so see KL25 Sub-Family Reference Manual (rev. I), Chapter 3 - Chip Configuration, Section 3.4.8. I DMA MUX Request Sources

| Source # | Module               | Description       |  |

|----------|----------------------|-------------------|--|

| 0        | -                    | Disabled          |  |

| 2-7      | UART0,1, 2           | Receive, Transmit |  |

| 16-19    | SPI0, 1              | Receive, Transmit |  |

| 22-23    | I <sup>2</sup> C0, 1 |                   |  |

| 24-29    | TPM0                 | Channels 0-5      |  |

| 32-35    | TPM1-2               | Channels 0-1      |  |

| 40       | ADC0                 |                   |  |

| 42       | CMP0                 |                   |  |

| 45       | DAC0                 |                   |  |

| 49-53    | Port Control Module  | Port A-E          |  |

| 54-56    | TPM0-2               | Overflow          |  |

| 57       | TSI                  |                   |  |

| 60-63    | DMAMUX               | Always enabled    |  |

## Triggering DMA Activity Using Peripherals

- Can use trigger events from peripherals to start DMA transfer

- Upon triggering, DMA can perform:

- One transfer (cycle steal mode)

- All transfers until BCR == 0 (continuous mode)

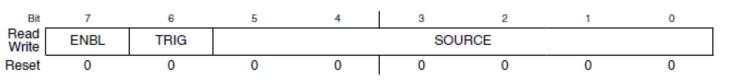

- DMA Multiplexer (DMAMUX)

- Selects which source will trigger a DMA channel

- Each DMA channel n has a configuration register DMAMUX\_CHCFGn

- ENBL: Enable DMA channel

- TRIG: Enables triggering of DMA channel

- SOURCE: Selects triggering source

DMAMUXx\_CHCFGn field descriptions

### **NC STATE** UNIVERSITY

### To Do

- Review development flow when does scheduler appear?

- Use same set of compute output data durations (d1-d5)

- Complete diagrams

- When to introduce task switching overhead?

- Complete text notes per slide

- (Convert diagrams from horizontal to vertical HW/SW split?)

### **NC STATE** UNIVERSITY

Interrupt entry/exit overhead

## N-Entry DAC Buffer with Empty Interrupt

### **NC STATE** UNIVERSITY

## Template for Software and Hardware Components and Timing

| Timer $\rightarrow$ DMA Trigger |  |  |

|---------------------------------|--|--|

| DMA IRQ                         |  |  |

| CPU Activity: ISR               |  |  |

| ISR →Task Trigger               |  |  |

| CPU Activity: Task              |  |  |

| Buffer A Timing Window          |  |  |

| Buffer A                        |  |  |

| Buffer B Timing Window          |  |  |

| Buffer B                        |  |  |

| DAC Code                        |  |  |

| DACV <sub>Out</sub>             |  |  |

### Software and Hardware

### Shield Audio Software and Hardware Architecture

### Shield Audio Software and Hardware Architecture

# ROUGH DIAGRAMS FROM ECE 560, MONDAY 9/23/24

C: Add 1-dement buffer