# PERFORMANCE ANALYSIS OF EXAMPLE APPLICATIONS ON PLATFORM 1 (RTC SCHEDULER WITH INTERRUPTS, BASIC PERIPHERAL USE)

V2 9/25/2025

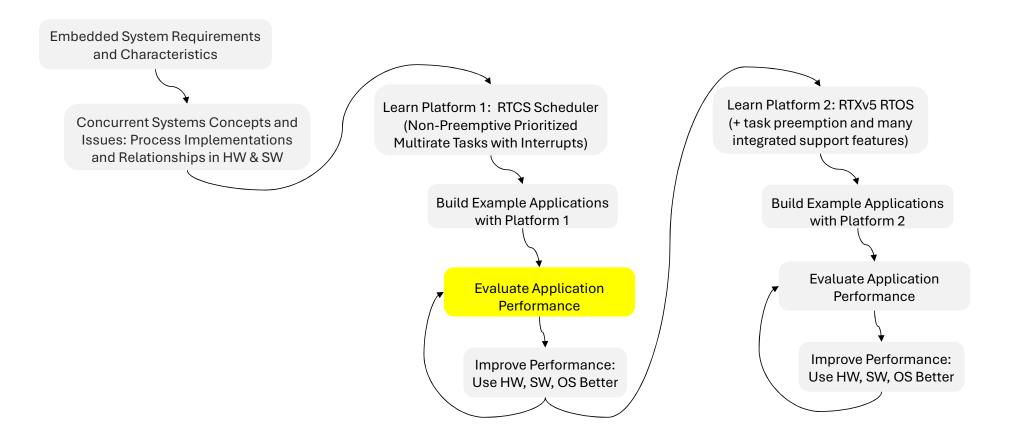

#### Where are we in the class?

## LN11 – Performance Analysis

- Summarize key characteristics of first implementations

- Processes, triggers (external sync), detectors, schedulers, workers, internal sync in workers

- Response time analysis to bound system interference

- ISR blocking by ISRs

- ISR preemption by ISRs

- Task blocking by tasks

- Task preemption by ISRs

- Tick ISR

- App ISRs?

- Characterize basic performance limits of Platform 1 (48 MHz CM0+)

- Interrupt System

- Latency: 15 clock cycles

- RTCS

- Time-triggered scheduling resolution

- Scheduler latencies: time to examine table, find next ready task

- Evaluate first implementations vs. performance limits

- Identify performance gaps and risks, mark in table

- Evaluate response times for first implementations vs. requirements

- Identify performance gaps and risks, mark in table

## PERFORMANCE ANALYSIS 1: RESPONSE TIME ANALYSIS

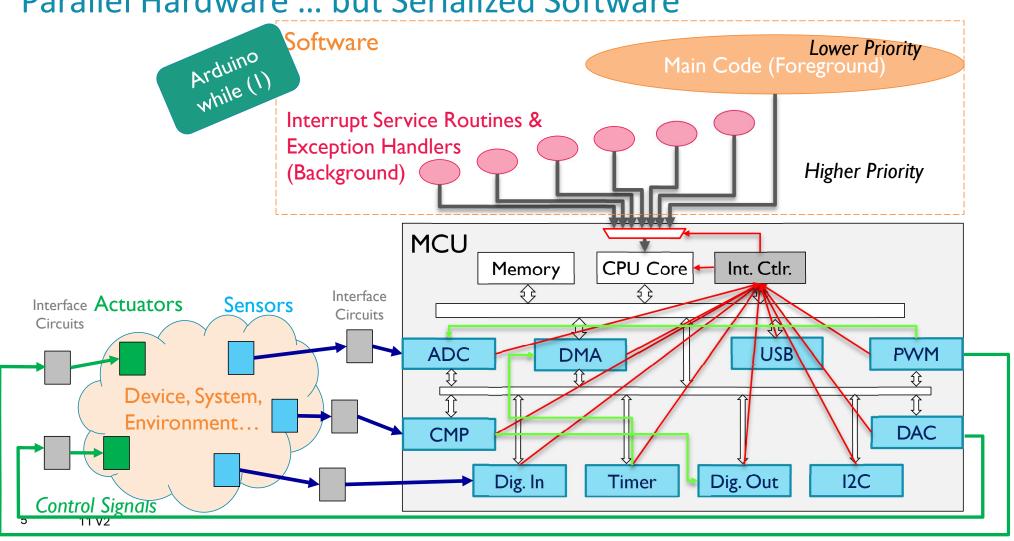

### Parallel Hardware ... but Serialized Software

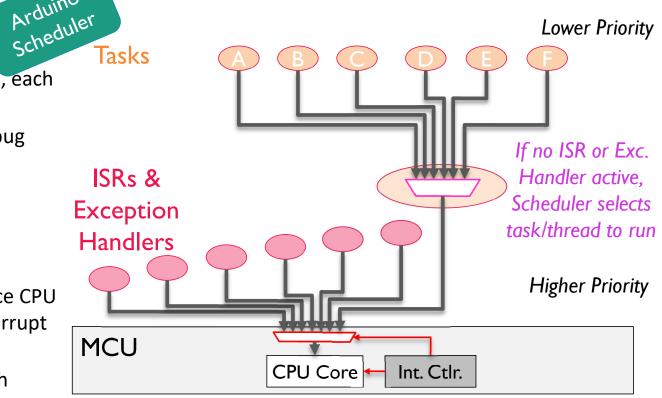

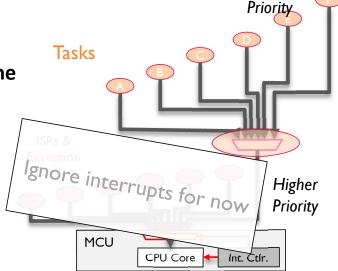

## Schedulers: Helping Software Share the CPU Better

- Build modular program

- Separate tasks/threads and ISRs, each running (mostly) independently

- Easier to develop, maintain, debug

- What code does CPU run?

- Normally CPU executes next instruction in program,

- But interrupt controller can force CPU to execute handler code for interrupt or exception request

- Task scheduler can decide which task/thread to run next

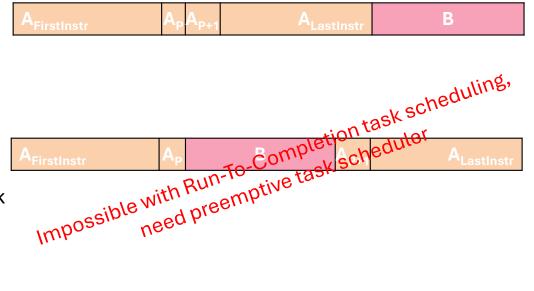

## Run-To-Completion Tasks and Task Preemption

- With run-to-completion task scheduling...

- Scheduler must wait for current task to complete before running another task

- Tasks cannot pause (or be preempted by other tasks) partway through, and later resume at that point within the task.

- If scheduler is running task A, it cannot

- Pause A partway through (after instruction A<sub>p</sub>),

- Switch in task B and run it,

- Resume task A partway through (at instruction A<sub>P+1</sub>)

- Preemptive task scheduler will support such task switching ...

- Letting task B preempt task A

- Letting task A yield the CPU and later pick up where it left off

## Responsiveness of While (1) Loop Scheduler

- Task A must run to service (handle) its event EvA

- EvA makes scheduler release task A

- Task A's response time (R<sub>△</sub>): How long from event EvA until task A finishes servicing it?

- Scheduler is While (1) loop

- Tasks run to completion.

- Fixed schedule: same task order every time

- Round-robin: each task gets same number of chances to run

- Scheduler behavior:

- EvA happened? Release A, run A until done.

- EvB happened? Release B, run B until done.

- EvC happened? Release C, run C until done.

- Continue for all events/tasks, then repeat with EvA

- Note

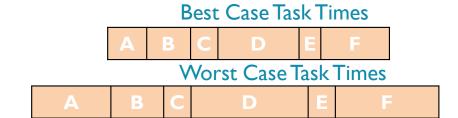

- We assumed each task takes a constant amount of time to execute

- Task i probably has range of possible execution times, between C<sub>i,Min</sub> and C<sub>i,Max</sub>

- Simplify timing model by making some worst-case performance assumptions

- Design for worst case, so assume task i always takes  $C_i = C_{i,Max}$

- Model will likely overestimate response time, but will never underestimate it so it will be safe.

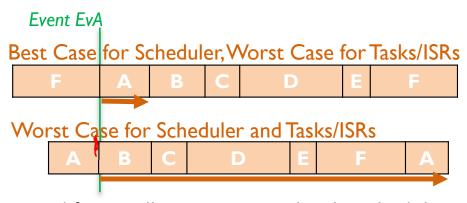

Event EvA

Lower

Responsiveness of While (1) Loop Scheduler

Task A's worst-case response time: What is the longest possible time from event EvA until task A finishes servicing it?

Depends on what code runs: ISRs scheduled by Interrupt Controller, tasks scheduled by task scheduler

- Simplify: Initially ignore time taken by scheduler, interrupt system and interrupt handlers.

- Best case: EvA happens just before scheduler checks it.  $R_A = C_A$

- Worst case: Every other event (EvB EvF) happens before scheduler checks EvA, and EvA happens just after that check:  $R_A = C_B + C_C + C_D + C_E + C_A$

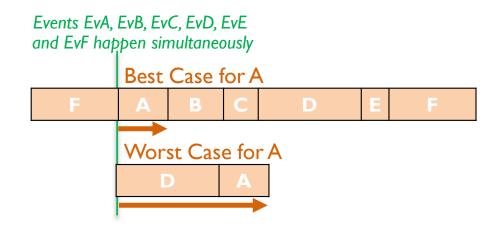

## Improvement: Prioritized Tasks

- Change scheduler to prioritize A > B > C etc.

- New behavior:

- If EvA happened, run A, then check for EvA again.

- Else if EvB happened, run B, then check for EvA again.

- Else if EvC happened, run C, then check for EvA again.

- Et cetera

- Implications

- Not round-robin. Now have dynamic (not static) schedule of task orders, since higher priority tasks get chance to run before lower priority tasks.

- Higher priority task may run multiple times before lower priority task gets to run once.

- There may be more events (and task releases) further delaying the start of a task.

- Best case for Task A: Same as before.  $R_{\Delta} = C_{\Delta}$

- Worst case for Task A (highest priority)?

- Delayed by longest task (D).  $R_A = C_A + Max(C_A, C_B, C_C, C_D, C_E, C_F)$

- Worst case for lower-priority tasks (B, C, D, E, F)?

- Also may be delayed by higher-priority tasks. Details on next slide.

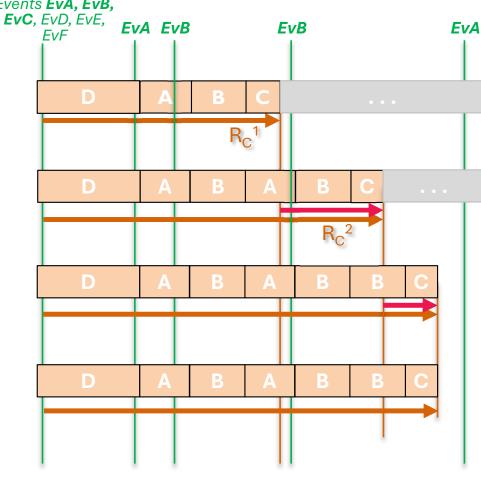

## What about Response Time for Lower Priority Tasks?

- First estimate  $(R_c^{-1})$  of response time  $R_c^{-1}$

- Task C's finish may be ...

- delayed by blocking once by longest task if already running:  $Max(C_A, C_B, C_C, C_D, C_F, C_F)$

- delayed at least once by each higher priority task (C<sub>A</sub>, C<sub>B</sub>)

- Equations

- $R_C^1 = \frac{Max(C_A, C_B, C_C, C_D, C_E, C_F)}{C_A + C_B} + \frac{C_C}{C_C}$

- Here:  $R_{c}^{1} = \frac{C_{D}}{C_{D}} + \frac{C_{A}}{C_{A}} + \frac{C_{B}}{C_{C}} + \frac{C_{C}}{C_{C}}$

- Second estimate  $(R_c^2)$

- More events for higher-priority tasks (A, B) may happen before C starts (during vulnerable time), leading to more releases before C can start

- R<sub>C</sub><sup>2</sup> = Max(C<sub>A</sub>, C<sub>B</sub>, C<sub>C</sub>, C<sub>D</sub>, C<sub>E</sub>, C<sub>F</sub>) +  $2*C_A + 2*C_B + C_C$ Here: R<sub>C</sub><sup>2</sup> = C<sub>D</sub>+  $2*C_A + 2*C_B + C_C$

- What if C still hasn't started when A or B is released again? Must *repeat* to see if A or B are released again during this additional vulnerable time

- Depends on minimum time between releases (EvA to EvA, EvB to EvB) in the worst case (burst)

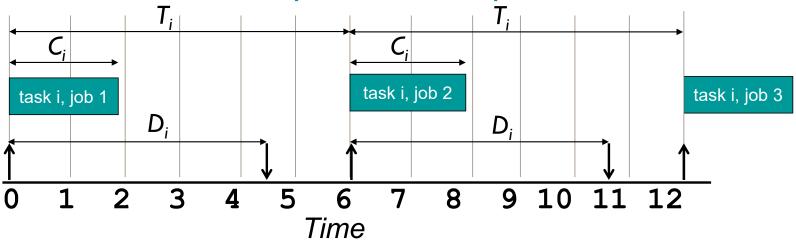

## Periodic Task Model of Computational Requirements

- Periodic Task Model describes characteristics for each task  $\tau_i$

- Job = a specific instance of that task running

- Task releases job so scheduler can run it

- A periodic task i releases a job every T<sub>i</sub> time units

- Job may have an absolute deadline  $D_i$  after its release

- Job takes a constant time  $C_i$  to execute

- Simplifying assumptions include

- no time needed for scheduler, task switching, ISR response/return

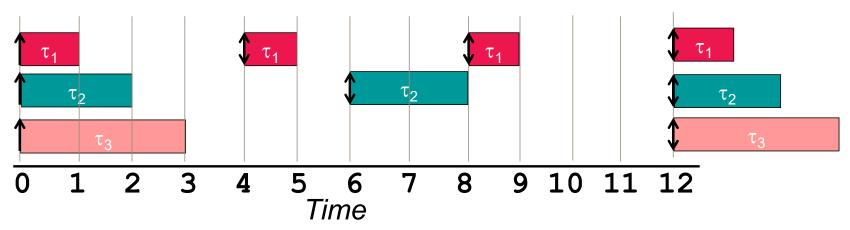

## Example Workload: What We Ask For

- Set of tasks with real-time requirements

- What gets executed when?

- Depends on scheduler and task priorities

| Task       | Exec.<br>Time <i>C<sub>i</sub></i> |    | Deadline<br>D <sub>i</sub> |

|------------|------------------------------------|----|----------------------------|

| $\tau_{I}$ | I                                  | 4  | 4                          |

| $\tau_2$   | 2                                  | 6  | 6                          |

| $\tau_3$   | 3                                  | 12 | 12                         |

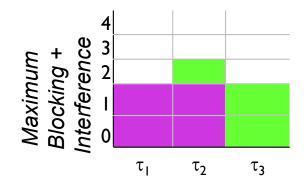

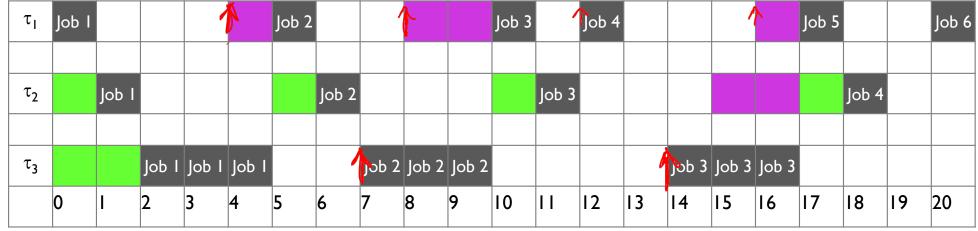

#### Scheduled Workload: What We Get

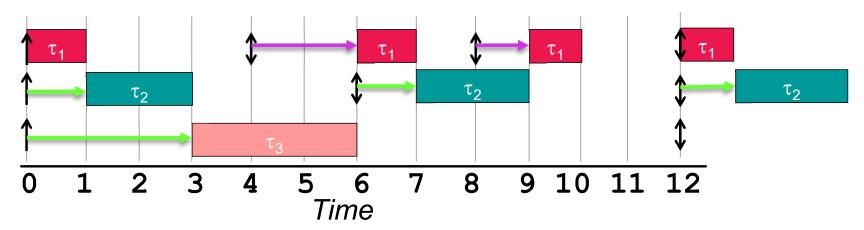

- Example: Scheduler and task fixed priorities

- Assign priorities as shown

- Use a non-preemptive scheduler

- What can delay a task?

- I: Interference caused by higher priority tasks

- B: Blocking caused by lower priority tasks

- Response time = Computation + Blocking + Interference

| Task     | Exec.<br>Time <i>C<sub>i</sub></i> | Period<br>T <sub>i</sub> | Deadline<br>D <sub>i</sub> | Priority |

|----------|------------------------------------|--------------------------|----------------------------|----------|

| $\tau_1$ | I                                  | 4                        | 4                          | High     |

| $\tau_2$ | 2                                  | 6                        | 6                          | Medium   |

| $\tau_3$ | 3                                  | 12                       | 12                         | Low      |

$R_i = C_i + B_i + I_i$

## Non-Preemptive Scheduling

| Task       | Exec.Time C <sub>i</sub> | Period T <sub>i</sub> | Priority |

|------------|--------------------------|-----------------------|----------|

| $\tau_{I}$ | I                        | 4                     | High     |

| $\tau_2$   | I                        | 5                     | Medium   |

| $\tau_3$   | 3                        | 7                     | Low      |

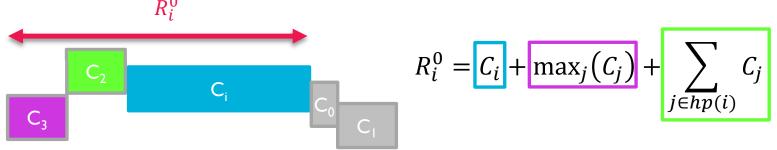

## **NUMERICAL RESPONSE TIME ANALYSIS**

### Numerical Response Time Analysis, Step 1

- How long could it take for task i to complete? What is its response time  $R_i$ ?

- Initial estimate based on worst case:

$R_i^0$  = computation time for task i + computation time for other tasks.

Non-prioritized scheduling: Every other task can run once

```

while (1) { for (j=0; j<NUM_TASKS; j++) { R_i^0 if (Tasks[j].RP > 0) { Tasks[j].RP--; Tasks[j].Task(); R_i^0 = C_i R_i^0 = C_i

```

Prioritized scheduling: All higher-priority tasks (+ longest task if non-preemptive) can run once

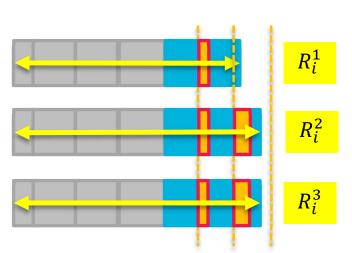

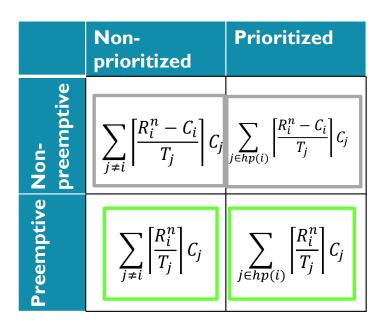

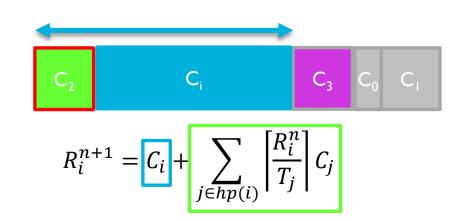

## Additional Timing Interference, Steps 2, 3, 4 ...

- Task i is vulnerable to delays from new job releases during vulnerable time

- Non-preemptive: 0 to R<sub>i</sub><sup>n</sup> C<sub>i</sub> since task i can't be preempted after it starts

Preemptive: 0 to R<sub>i</sub><sup>n</sup> since

higher-priority task can preempt task i

- Consider new releases to update completion time estimate  $R_i^{n+1}$

- Repeat until no new releases, or any deadline (if present) is missed

## How Many $T_i$ Releases Possible During Vulnerable Time?

- Initial estimate was one release, so task's time is one job:  $1*C_i$

- Remaining estimates must consider all job releases possible during vulnerable time: Ceiling(vulnerable time /  $T_j$ )\* $C_j$

$$R_i^0 = \boxed{C_i} + \boxed{\sum_{j \neq i} C_j}$$

$$R_i^0 = C_i + \max_j (C_j) + \sum_{j \in hp(i)} C_j$$

## Response Time: Indep. Tasks with Task Preemption + Prioritization

- Preemption ...

- Eliminates blocking of task i by lower-priority independent tasks.

- Allows higher-priority tasks to preempt task i

## SUMMARY OF APPLICATION DESIGN APPROACHES

## **Example Application and Subsystem Processes**

- 1. Quadrature Decoder w/Limit Switch

- 2. Waveform Generator

- 3. Blinky Control Panel

- 4. Touchscreen

- Serial UART Communications

- LCD Controller

- Scope

- 8. SMPS Controller

- 9. More Comms

- 1. SPI

- 2. Higher protocol layers: I<sup>2</sup>C, Secure Digital via SPI

## Applications: Functionality First, then Performance

|                                               |       |                                          | Quad. Dec.<br>w/Z Limit<br>Switch | Waveform<br>Generator                 | Blinky<br>Control<br>Panel | Touch screen      | Serial<br>Comms.                                     | LCD<br>Controller    | Scope                                                     | SMPS Controller               | I <sup>2</sup> C Comms.                                                   | μSD via SPI<br>Comms.                          |

|-----------------------------------------------|-------|------------------------------------------|-----------------------------------|---------------------------------------|----------------------------|-------------------|------------------------------------------------------|----------------------|-----------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------|------------------------------------------------|

|                                               | 00    | Simple Digital                           | In                                |                                       | In, Out                    | Out               |                                                      |                      |                                                           | PWM Out                       |                                                                           |                                                |

|                                               | lij   | Complex Digital                          |                                   |                                       | PWM                        |                   | In, Out                                              | Bus Out              |                                                           |                               | In, Out                                                                   | In, Out                                        |

| Interfacin                                    |       | Analog                                   |                                   | Out                                   | ADC In, CMP<br>In, DAC Out | ADC In            |                                                      |                      | ADC In,<br>Cmp In                                         | ADC In with Sync.<br>Sampling |                                                                           |                                                |

| ality                                         | Async | # Processes for async. exec.             | 1,2                               | 1,2                                   | 4                          | 0, 1              | 2                                                    | 0                    | 1,2                                                       | 1                             | 1                                                                         | 2                                              |

| Providing Functionality                       |       | Sync and Do:<br>Coarse Triggering        | Digital Edge<br>Detection         | Periodic<br>Output<br>Updates         |                            |                   | Tx Rdy, Rx<br>Done events.<br>Producer &<br>Consumer |                      | Ana. Edge Det.,<br>Periodic In.<br>Smplg., Buffer<br>mgt. | ADC In with Sync.<br>Sampling | Data Producers &<br>Consumers. I2C<br>Device read<br>response.            | Tx Rdy, Rx<br>Done events.<br>Prod. &<br>Cons. |

| Providing<br>Sync and .                       |       | Internal, Fine Grain<br>Block/Sched/Trig |                                   |                                       | ADC conv.<br>time          | ADC conv.<br>time | When to notify receiver?                             |                      |                                                           |                               | I2C message internal<br>events & timing<br>reqts. for conditions,<br>data |                                                |

|                                               |       | Tx, Rx byte queues                       |                                   | LCD Ctlr Sharing,<br>Data buffer mgt. |                            | Tx, Rx Msgs       | Tx, Rx byte queues                                   |                      |                                                           |                               |                                                                           |                                                |

| Inter-Process Comm.  Shared Position Variable |       |                                          |                                   |                                       |                            |                   | Data buffer                                          |                      |                                                           |                               |                                                                           |                                                |

| လွ                                            |       | Timing Stability                         |                                   | 1                                     | 1                          |                   |                                                      |                      | 2                                                         | 1                             |                                                                           |                                                |

| edt                                           |       | Responsiveness                           |                                   |                                       | 1                          |                   |                                                      |                      | 1                                                         | 1                             |                                                                           | 1                                              |

| Meeting Perf. Reqts.                          |       | Reducing SW<br>Overhead                  |                                   | 2                                     |                            |                   |                                                      | 1- Perf.<br>Optimiz. | 2                                                         | 2                             | 1 – series of timed<br>I/O events per<br>message. FSM vs.<br>RTOS         |                                                |

| Mee                                           |       | Tolerating Timing<br>Mismatches          |                                   | 2                                     |                            |                   | 2                                                    |                      | 2                                                         |                               |                                                                           | 2                                              |

## **Example Application Data**

| Application                    | Independent Process? | Triggers                                                     | Trigger Detection       | Scheduler                    | Work done in     | Internal Sync. #1 in Work<br>Code       | Internal Sync. #2 in Work<br>Code       |

|--------------------------------|----------------------|--------------------------------------------------------------|-------------------------|------------------------------|------------------|-----------------------------------------|-----------------------------------------|

| Quadrature Decoder             | Υ                    | Events: ↑A, ↑Z                                               | Peripheral (PORT)       | Interrupt System             | ISR(s) for A, Z  | -                                       |                                         |

| Waveform Generator             | Υ                    | Time - Periodic: T <sub>sample</sub>                         | RTCS Tick Handler       | RTCS                         | Task_Update_DAC  | -                                       |                                         |

|                                | Υ                    | Time - Periodic: T <sub>Poll</sub>                           | RTCS Tick Handler       | RTCS                         | Task_On_Off      | -                                       |                                         |

|                                | Υ                    | Time - Periodic: T <sub>Poll</sub>                           | RTCS Tick Handler       | RTCS                         | Task_Level_Alarm | -                                       |                                         |

| Blinky Control Panel           | Υ                    | Time - Periodic: T <sub>Poll</sub>                           | RTCS Tick Handler       | RTCS                         | Task_Dimmer      | Wait for A/D conversion to complete     |                                         |

|                                | Υ                    | Time - Periodic: T <sub>Flash</sub>                          | RTCS Tick Handler       | RTCS                         | Task_Flash       | -                                       |                                         |

| Touchscreen                    | Υ                    | Time - Periodic: T <sub>Poll</sub>                           | RTCS Tick Handler       | RTCS                         |                  | Wait for 1st A/D conversion to complete | Wait for 2nd A/D conversion to complete |

| Serial UART Comms.             | Υ                    | Events: UART Tx events                                       | Peripheral (UART)       | Interrupt System             | ISR for Tx       | -                                       |                                         |

| Serial OAKT Collins.           | Υ                    | Events: UART Rx events                                       | Peripheral (UART)       | Interrupt System             | ISR for Rx       | -                                       |                                         |

| LCD Controller                 | N                    | When called by process                                       | n/a                     | n/a                          |                  | Not needed.                             |                                         |

|                                | Υ                    | Event: $V_{ln} \uparrow V_{Trigger}$                         | Software polling of ADC | ?                            | Detect Trigger   | Wait for A/D conversion complete        |                                         |

| Oscilloscope                   |                      | Trigger detected and Time -<br>Periodic: T <sub>Sample</sub> | ?                       | ?                            | Sample Data      | Wait for A/D conversion complete        |                                         |

|                                |                      | Sample Data completes                                        |                         |                              | Plot Data        | -                                       |                                         |

| SMPS Controller                | Υ                    | Event: PWM Timer Phase<br>Reference                          | Peripheral (ADC)        | (direct hardware connection) | ADC Peripheral   |                                         |                                         |

| Sirra Controller               | Υ                    | Event: A/D Conversion<br>Completed                           | Peripheral (ADC)        | Interrupt System             | ISR for ADC      | Not needed.                             |                                         |

| I <sup>2</sup> C Comms.        | Y                    | Events: I <sup>2</sup> C message<br>components               |                         |                              |                  |                                         |                                         |

| μSD via SPI Comms.<br>24 11 V2 | Υ                    | Events: Data Exchange events                                 |                         |                              |                  | Many: SD Ctlr delays                    |                                         |

## PERFORMANCE ANALYSIS 2: PLATFORM LIMITS

### Platform 1 Performance Limits

- Characterize basic performance limits of Platform 1 (48 MHz Cortex-M0+)

- Interrupt System

- Latency: 15 clock cycles

- RTCS

- Time-triggered scheduling resolution: 1 tick

Scheduler latencies: time to examine table, find next ready task, call task function

## **Evaluation of First Implementations**

Identify performance gaps, limits, and risks, mark in table

| identity per            |

|-------------------------|

| Application             |

| Quadrature Decoder      |

| Waveform Generator      |

| Blinky Control Panel    |

| Touchscreen             |

| Serial UART Comms.      |

| LCD Controller          |

| Oscilloscope            |

| SMPS Controller         |

| I <sup>2</sup> C Comms. |

| μSD via SPI Comms.      |

|                         |