## Lecture 03 Notes -I/O, Timing and Synchronization

## Overview

- A. Timing requirements for I/O activities are major driver for embedded system design decisions

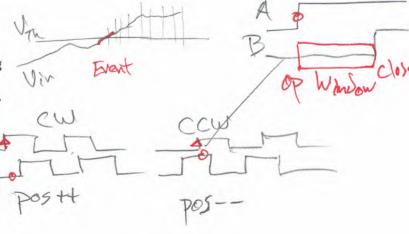

- B. May need to synchronize to event or time before doing the work (Sync and Do)

- 1. Scope trigger: detect input rising across threshold voltage, then can start sampling

- 2. Quadrature decoder: detect input A rising, then sample input B, increment or decrement count

## II. Understanding Process Chain for I/O Activities

- A. Synchronize with something

- 1. Types

- a. Event-Triggered: Detect event

- b. Time-Triggered: Await target time

- B. Do processing in response

- 1. Timing requirements:

- a. Simple deadline: within TDL of event/time

- b. Window deadline: Between TDL\_Open and T<sub>DL\_Close</sub> of event/time

- C. Repeat?

- activities, so next will sync (event or time) to next part or do it immediately/ASAP

- 2. Examples inputs:

1. May have burst or sequence of I/O

a. Quadrature decoder,

b. UART receive data

| III. How to Synchronize?  A. All Hardware  1. Easy: Dedicated signals  B. Some Software  1. HW/SW allocation and processing chain. SW polls hardware (input peripheral)  2. Hard, since software timing is sloppy, gets even harder when sharing CPU  a. Timing variation diagram (ramp), sync to stabilize/cut timing variation | SW PA DOUT POUT PORT Avalog V-to Digital to Hualog |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 3. Start simple: Not sharing CPU  a. Detect with blocking SW loop polling (busy-waiting)  b. Responsiveness  c. Greedy!  Sync Proc/Haude                                                                                                                                                                                         | Dy > GP10 DINT SW<br>Ava > 9+ Ana > ADC<br>Rowt    |

| 4. Share CPU with software scheduling method  a. Round-Robin Loop/Cyclic Exec.  i. Detector doesn't block, but take turns with other code (possibly multiple detectors)  ii. Responsiveness  iii. Not so greedy                                                                                                                  | Handle Q2  Handle Q2  Handle Q2  Handle Q2         |

| b. Many other sharing options. Prioritization, preemption  i. + Schedule, dispatch.  C. HW Event Detection  1. Hardware peripheral detects event  2. HW/SW allocation and processing chain. SW polls event detector                                                                                                              | - Run it  Sync Handle                              |

| D. HW Event Detection + Interrupt System  1. HW/SW allocation and processing chain                                                                                                                                                                                                                                               | Ev. Det. Handler Isage                             |

2. Handler runs

|    |                        |                                                      | 2             |          |            |           |               |

|----|------------------------|------------------------------------------------------|---------------|----------|------------|-----------|---------------|

|    |                        | ning Analysis                                        |               |          |            |           |               |

| A. | Approach<br>1. Slack t |                                                      |               |          |            |           |               |

|    |                        | ow late can process star                             | t and most    |          |            |           |               |

|    |                        | adline?                                              | t and meet    |          |            |           |               |

|    | ^                      | LA                                                   | -             | -0       |            |           |               |

|    | 1                      | sleck Time                                           | $\rightarrow$ | V        |            |           |               |

|    | 2. Respor              | nse time                                             |               |          |            |           |               |

|    | a. Wh                  | hen will this process fini                           | sh,           |          |            |           |               |

|    |                        | nsidering effects of othe<br>system                  | r processes   |          |            |           |               |

|    |                        | 4                                                    | 1.            |          |            |           |               |

|    | 1                      |                                                      | V             | 1        |            |           |               |

|    |                        | The state of                                         |               | V        |            |           |               |

|    | F                      | -                                                    | 1             | preempth | on         |           |               |

| В. |                        | tions from scheduler s                               |               |          | . 7        | 110       |               |

|    |                        | ng SW processes sche<br>static fixed schedule        | duler         | ARC      | DAB        | - C 13    |               |

|    |                        | nic scheduling – differen                            | orders        | 11 13 0  | 11         | TMCA      | AA            |

|    | possibl                |                                                      | orders        | ABA      | CADA       | DAC       |               |

| •  | a. Pri                 | oritize SW procs                                     |               | - 3 -    |            |           |               |

|    | i.                     | Static or dynamic?                                   |               |          |            |           |               |

|    | ii.                    | Timing-based or other?                               |               |          |            |           |               |

|    |                        |                                                      |               |          |            |           |               |

|    |                        |                                                      |               |          |            |           |               |

|    |                        |                                                      |               |          |            |           |               |

|    | 3. Preemp              | otion of SW proc                                     |               |          |            |           |               |

|    |                        | interrupt service routine                            | s             |          |            |           |               |

|    | b. By                  | other SW processes                                   |               |          |            |           |               |

|    |                        |                                                      |               | 1        |            |           |               |

|    | ,                      |                                                      | 1-            |          |            |           |               |

|    |                        |                                                      |               |          | .~         | /         | Λ.            |

|    | 4. Results             | s: timing delays                                     |               | 1 /      | Hrio las   | k-Inter   | temce         |

|    |                        | erference by same, high                              | er-priority   | M        | -1         |           |               |

|    |                        | processes                                            |               | 8        | Task       | 1         | Λ Λ           |

|    | b. Blo                 |                                                      | 1             | 2        | 1 Di       | Tock-Sha  | red mesource  |

|    |                        | Non-preemptive sched                                 |               | 1/ 11    | m LOW-LINE | ) (W)     | L . \         |

|    |                        | by lower-priority SW pro<br>sharing resource with th |               | Plog     | Scheoule   | es (Not P | need Mesource |

|    |                        |                                                      |               |          |            |           |               |